# **ATC2603C Datasheet**

Version: 2.2

2015-09-23

### **Declaration**

#### **Disclaimer**

Information given in this document is provided just as a reference or example for the purpose of using Actions' products, and cannot be treated as a part of any quotation or contract for sale.

Actions products may contain design defects or errors known as anomalies or errata which may cause the products' functions to deviate from published specifications. Designers must not rely on the instructions of Actions' products marked "Reserved" or "undefined". Actions reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

ACTIONS DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL EXPRESS OR IMPLIED WARRANTIES OF MERCHANTABILITY, ACCURACY, SECURITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT OF INTELLECTUAL PROPERTY AND THE LIKE TO THE INFORMATON OF THIS DOCUMENT AND ACTIONS PRODUCTS.

IN NO EVENT SHALL ACTIONS BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES WHATSOEVER, INCLUDING, WITHOUT LIMITATION FOR LOST OF DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND ARISING FROM USING THE INFORMATON OF THIS DOCUMENT AND ACTIONS PRODUCTS. REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF ACTIONS OR OTHERS; STRICT LIABILITY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER ACTIONS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES OR NOT.

Actions' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Actions and further testing and/or modification will be fully at the risk of the customer.

#### Ways of obtaining information

Copies of this document and/or other Actions product literature, as well as the Terms and Conditions of Sale Agreement, may be obtained by visiting Actions' website at: <a href="http://www.actions-semi.com">http://www.actions-semi.com</a> or from an authorized Actions representative.

#### **Trademarks**

The word "Actions" and the logo are the trademarks of Actions Semiconductor Co., Ltd, and Actions (Zhuhai) Technology Co., Limited is authorized to use them. Word "炷芯" is the trademark of Actions (Zhuhai) Technology Co., Limited. Names and brands of other companies and their products that may from time to time descriptively appear in this document are the trademarks of their respective holders, no affiliation, authorization, or endorsement by such persons are claimed or implied except as may be expressly stated therein.

### **Rights Reserved**

The provision of this document shall not be deemed to grant buyers any right in and to patent, copyright, trademark, trade secret, know how, and any other intellectual property of Actions or others.

#### Miscellaneous

Information contained or described herein relates only to the Actions products and as of the release date of this publication, abrogates and supersedes all previously published data and specifications relating to such products provided by Actions or by any other person purporting to distribute such information.

Actions reserves the rights to make changes to information described herein at any time without notice. Please contact your Actions sales representatives to obtain the latest information before placing your product order.

### **Additional Support**

Additional product and company information can be obtained by visiting the Actions website at: <a href="http://www.actions-semi.com">http://www.actions-semi.com</a>

## **Contents**

| D | ecla  | ration ·           |                                                                 | ii |

|---|-------|--------------------|-----------------------------------------------------------------|----|

| C | onte  | nts····            |                                                                 | iv |

| R | evisi | on Hist            | History                                                         |    |

| 1 | In    | troduc             | ion·····                                                        | 1  |

|   | 1.1   | Overv              | ew                                                              | 1  |

|   | 1.2   |                    |                                                                 | 1  |

|   | 1.3   | Typica             | l Applications ·····                                            | 3  |

|   | 1.4   | Orderi             | ag Information · · · · · · · · · · · · · · · · · · ·            | 3  |

| 2 | A     | hsolute            | Maximum Rating                                                  | .4 |

| _ |       |                    |                                                                 | •  |

| 3 | R     | ecomm              | ended Operating Conditions ···································· | 4  |

| 4 | E     | lectrical          | Characteristics ·····                                           | 5  |

|   | 4.1   |                    |                                                                 | 5  |

|   |       |                    |                                                                 |    |

|   | 4.2   |                    |                                                                 |    |

|   | 4.3   |                    |                                                                 |    |

|   | 4.4   | LDO ·              |                                                                 | 7  |

|   | 4.5   | Typica             | l Characteristics · · · · · · · · · · · · · · · · · · ·         | 11 |

|   | 4.6   |                    |                                                                 |    |

|   | 4.7   | Load 7             | ransient Response                                               | 12 |

|   |       |                    |                                                                 |    |

| 5 | A     | udio Co            | dec Subsystem ····· 1                                           | .4 |

|   | 5.1   |                    |                                                                 |    |

|   | 1     | _                  |                                                                 |    |

|   |       | _                  | -                                                               |    |

|   |       | 5.1.2.1<br>5.1.2.2 |                                                                 |    |

|   |       | 5.1.2.3            |                                                                 |    |

|   |       | 5.1.2.4            | _                                                               |    |

|   |       | 5.1.2.5            | =                                                               |    |

|   |       | 5.1.2.6            | _                                                               |    |

|   |       | 5.1.2.7            | DAC_ANALOG3 ·····                                               | 20 |

|   |       | 5.1.2.8            | _                                                               |    |

|   |       | 5.1.2.9            | ADC_HPFCTL ·····                                                | 21 |

|   | 5.1.   | 2.10 ADC_CTL                                                               | · 22 |

|---|--------|----------------------------------------------------------------------------|------|

|   | 5.1.   | .2.11 AGC_CTL0                                                             | · 23 |

|   | 5.1.   | .2.12 AGC_CTL1                                                             | 25   |

|   | 5.1.   | 2.13 AGC CTL2 ·····                                                        | . 26 |

|   | 5.1.   | .2.14 ADC ANALOG0                                                          | . 27 |

|   | 5.1.   | .2.15 ADC ANALOG1                                                          | . 29 |

|   |        | _                                                                          |      |

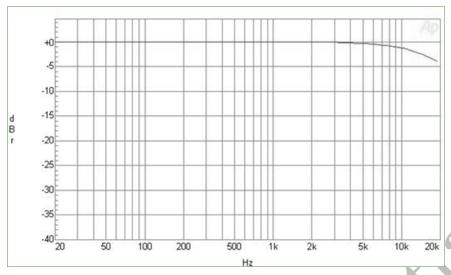

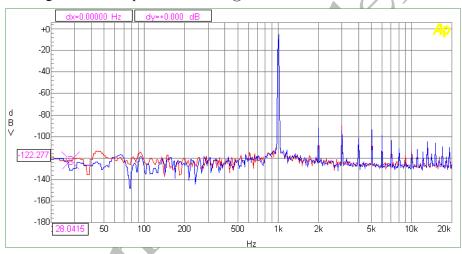

|   |        | Audio Characteristics                                                      |      |

|   | 5.2.1  | DAC+PA ····                                                                |      |

|   | 5.2.2  | PA                                                                         | -    |

|   | 5.2.3  | ADC                                                                        | -33  |

| 6 | TWI    | Interface ·····                                                            | 34   |

| U |        |                                                                            | 54   |

|   | 6.1 F  | Features                                                                   | · 34 |

|   | 6.2 R  | Register List ·····                                                        | · 34 |

|   | 62 D   | Register Description ·····                                                 | 25   |

|   | 6.3 R  | SADDR                                                                      |      |

|   | 0.3.1  | SADDR                                                                      | . 33 |

| 7 | Powe   | er Management Unit·····                                                    | 36   |

| • |        | · · · · · · · · · · · · · · · · · · ·                                      |      |

|   | 7.1 F  | Features                                                                   | . 36 |

|   | 7.2 N  | Module Description  DC-DC Module  LDO Module                               | · 36 |

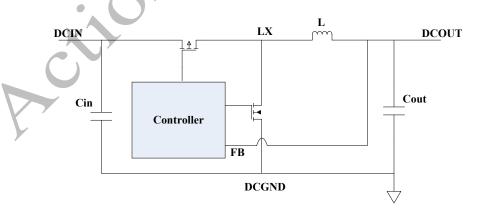

|   | 7.2.1  | DC-DC Module · · · · · · · · · · · · · · · · · · ·                         | · 36 |

|   | 7.2.2  | LDO Module · · · · · · · · · · · · · · · · · · ·                           | . 37 |

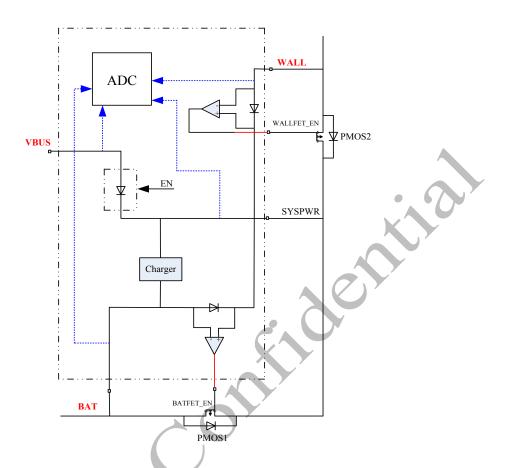

|   | 7.2.3  | Charger Module · · · · · · · · · · · · · · · · · · ·                       | · 38 |

|   | 7.2.4  | APDS Module ·····                                                          | . 39 |

|   | 7.2.5  | Power Modes · · · · · · · · · · · · · · · · · · ·                          | 40   |

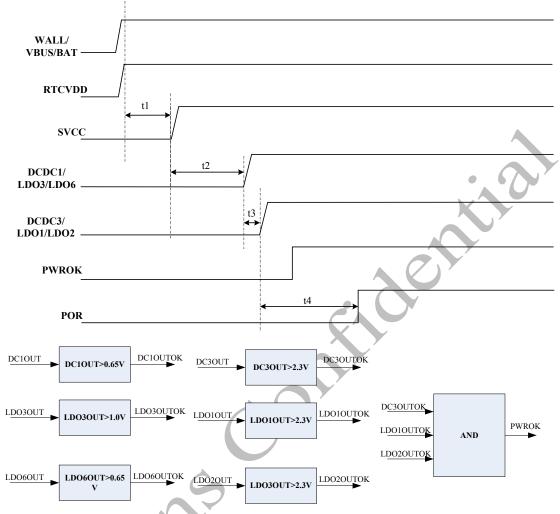

|   | 7.2.6  | POR and Power ON/OFF Sequence Module · · · · · · · · · · · · · · · · · · · | · 41 |

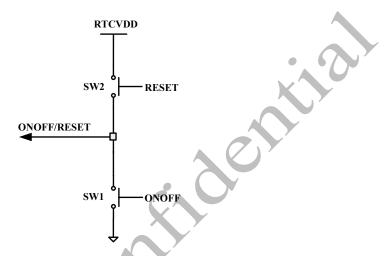

|   | 7.2.7  | ONOFF & Reset Module ····                                                  | · 42 |

|   | 7.2.8  | PWM Module ····                                                            | 42   |

|   | 7.3 R  | Register List ····                                                         | . 42 |

|   |        |                                                                            |      |

|   | 7.4 R  | Register Description ·····                                                 |      |

|   | 7.4.1  | PMU_SYS_CTL0 ·····                                                         |      |

|   | 7.4.2  | PMU_SYS_CTL1                                                               |      |

|   | 7.4.3  | PMU_SYS_CTL2 ····                                                          |      |

|   | 7.4.4  | PMU_SYS_CTL3 ····                                                          |      |

|   | 7.4.5  | PMU_SYS_CTL4 ····                                                          |      |

|   | 7.4.6  | PMU_SYS_CTL5 ····                                                          |      |

|   | 7.4.7  | PMU_BAT_CTL0 ····                                                          |      |

|   | 7.4.8  | PMU_BAT_CTL1 ·····                                                         |      |

|   | 7.4.9  | PMU_VBUS_CTL0 ·····                                                        |      |

|   | 7.4.10 | <u> </u>                                                                   |      |

|   | 7.4.11 | PMU_WALL_CTL0·····                                                         | · 54 |

|   | 7.4.12 | PMU WALL CTL1·····                                                         | . 55 |

| 7.4.13 | PMU_SYS_PENDING ·····                                   | 56     |

|--------|---------------------------------------------------------|--------|

| 7.4.14 | PMU_DC1_CTL0 ·····                                      | 57     |

| 7.4.15 | PMU_DC2_CTL0 ····                                       | 59     |

| 7.4.16 | PMU_DC3_CTL0 ····                                       | 59     |

| 7.4.17 | PMU_LDO1_CTL·····                                       | 61     |

| 7.4.18 | PMU_LDO2_CTL·····                                       | 62     |

| 7.4.19 | PMU_LDO3_CTL·····                                       | 62     |

| 7.4.20 | PMU_LDO5_CTL·····                                       | 63     |

| 7.4.21 | PMU_LDO6_CTL·····                                       | 63     |

| 7.4.22 | PMU_LDO7_CTL·····                                       | 64     |

| 7.4.23 | PMU_LDO11_CTL ·····                                     | 64     |

| 7.4.24 | PMU_SWITCH_CTL ·····                                    | 65     |

| 7.4.25 | PMU_OV_CTL0·····                                        | 66     |

| 7.4.26 | PMU_OV_CTL1·····                                        | 67     |

| 7.4.27 | PMU_OV_STATUS ·····                                     | 68     |

| 7.4.28 | PMU_OV_EN·····                                          | 69     |

| 7.4.29 | PMU_OV_INT_EN ·····                                     | 69     |

| 7.4.30 | PMU_OC_CTL ·····                                        | 70     |

| 7.4.31 | PMU_OC_STATUS ·····                                     | 72     |

| 7.4.32 | PMU_OC_EN ·····                                         | 73     |

| 7.4.33 | PMU_OC_INT_EN ·····                                     | 73     |

| 7.4.34 | PMU_UV_CTL0·····                                        | 74     |

| 7.4.35 | PMU_UV_CTL1·····                                        | 75     |

| 7.4.36 | PMU_UV_STATUS ······                                    | 76     |

| 7.4.37 | PMU_UV_EN·····                                          | 77     |

| 7.4.38 | PMU_UV_INT_EN ······                                    | ··· 78 |

| 7.4.39 | PMU_OT_CTL ·····                                        | 78     |

| 7.4.40 | PMU_CHARGER_CTL0·····                                   | 79     |

| 7.4.41 | PMU_CHARGER_CTL1·····                                   | 81     |

| 7.4.42 | PMU_CHARGER_CTL2·····                                   | 82     |

| 7.4.43 | PMU_APDS_CTL·····                                       | 83     |

| 7.4.44 | PMU_ICMADC ·····                                        | 85     |

| 7.4.45 | PMU_ABNORMAL_STATUS ·····                               | 85     |

| 7.4.46 | PMU_WALL_APDS_CTL · · · · · · · · · · · · · · · · · · · | 86     |

| 7.4.47 | PMU_REMCON_CTL0 ·····                                   | 87     |

| 7.4.48 | PMU_REMCON_CTL1 ·····                                   | 88     |

| 7.4.49 | PMU_MUX_CTL0·····                                       | 89     |

| 7.4.50 | PMU_SGPIO_CTL0 ·····                                    | 90     |

| 7.4.51 | PMU_SGPIO_CTL1 ·····                                    | 91     |

| 7.4.52 | PMU_SGPIO_CTL2 ·····                                    | 91     |

| 7.4.53 | PMU_SGPIO_CTL3 ·····                                    | 92     |

| 7.4.54 | PMU_SGPIO_CTL4 ·····                                    | 93     |

| 7.4.55 | PWMCLK_CTL ·····                                        | 93     |

| 7.4.56 | PWM0_CTL····                                            | 94     |

| ,          | .57 PWM1_CTL·····                                        | 94 |

|------------|----------------------------------------------------------|----|

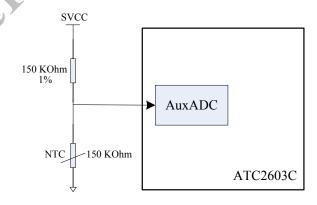

| 8          | ıxiliary ADC·····                                        | 95 |

| 8.1        | Module Description                                       | 95 |

| 8.2        | Register List · · · · · · · · · · · · · · · · · · ·      | 96 |

| 8.3        | Register Description                                     | 97 |

| :          | .1 PMU_AUXADC_CTL0 ·····                                 | 97 |

| ;          | .2 PMU_AUXADC_CTL1 ·····                                 | 98 |

| :          | .3 PMU_BATVADC ·······                                   | 99 |

| 8          | .4 PMU_BATIADC······                                     | 99 |

| :          | .5 PMU_WALLVADC 1                                        | 00 |

| :          | =                                                        | 00 |

| :          | .7 PMU_VBUSVADC······· 1                                 | 00 |

| 8          | .8 PMU_VBUSIADC ······ 1                                 | 00 |

| 8          | .9 PMU_SYSPWRADC ······                                  |    |

| 8          | .10 PMU_REMCONADC ······                                 | 01 |

| 8          | .11 PMU_SVCCADC ······ 1                                 | 01 |

| ;          | .12 PMU_CHGIADC ····· 1                                  | 01 |

| ;          | .13 PMU_IREFADC                                          | 01 |

| 8          | .14 PMU_BAKBATADC ····· 1                                | 02 |

| 8          | .14 PMU_BAKBATADC                                        | 02 |

| 8          | .15 PMU_ICTEMPADC                                        | 02 |

| 8          |                                                          |    |

| 8          | .18 PMU_AUXADC2 ····· 1                                  |    |

| 8          | .19 PMU_ADC_DBG0 ····· 1                                 |    |

|            | .20 PMU_ADC_DBG1 · · · · · · · · · · · · · · · · · · ·   |    |

|            | .21 PMU_ADC_DBG2 · · · · · 1                             |    |

| 8          | .22 PMU_ADC_DBG3 1                                       |    |

| 8          | .23 PMU_ADC_DBG4 · · · · 1                               | 03 |

| <b>9</b> ] | eal-Time Clock · · · · · · · 10                          | Ո4 |

|            | Module Description · · · · · · · · · · · · · · · · · · · |    |

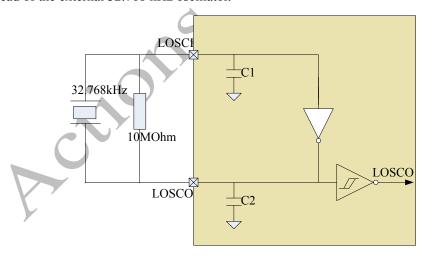

| 9.1        | .1 32kHz Oscillator                                      |    |

|            | .2 Calendar · · · · · · · · · · · · · · · · · · ·        |    |

|            | 3 Alarm                                                  |    |

|            |                                                          |    |

| 9.2        | Register List                                            | 05 |

| 9.3        | Register Description 1                                   | 06 |

| 9          | .1 RTC_CTL                                               |    |

| 9          | .2 RTC_MSALM ····· 1                                     |    |

| 9          | .3 RTC_HALM·····                                         | 07 |

| 9          | .4 RTC_YMDALM ····· 1                                    |    |

| 9          | .5 RTC_MS ····· 1                                        |    |

| 9          | .6 RTC_H ····· 1                                         | 08 |

|    | 9.3.7       | ' R' | TC_DC ····                                              | 108      |

|----|-------------|------|---------------------------------------------------------|----------|

|    | 9.3.8       | R'   | TC_YMD                                                  | 108      |

|    |             |      |                                                         |          |

| 10 | Infr        | are  | d Remote Controller ······1                             | 10       |

| 1  | 0.1         | Feat | ures····                                                | 110      |

| 1  | 0.2         | Mod  | lules Description·····                                  | 110      |

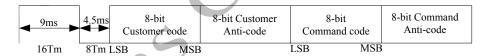

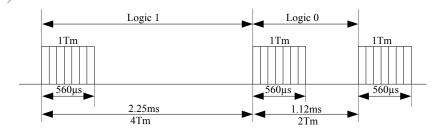

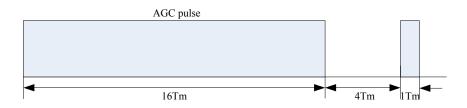

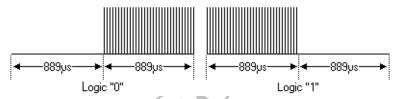

|    | 10.2        |      | 9012 Protocol · · · · · · · · · · · · · · · · · · ·     |          |

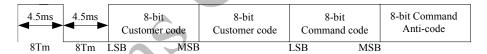

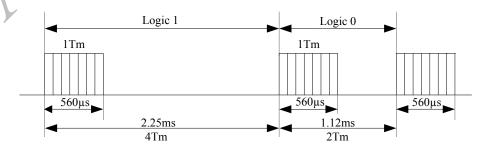

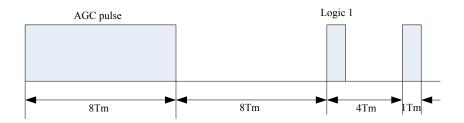

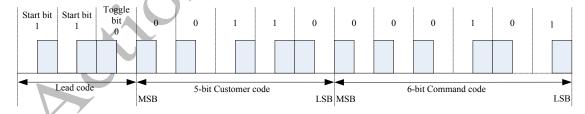

|    | 10.2        | .2   | NEC Protocol (8-bit) ·····                              | 111      |

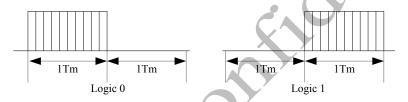

|    | 10.2        | .3   | RC5 Protocol ····                                       | 112      |

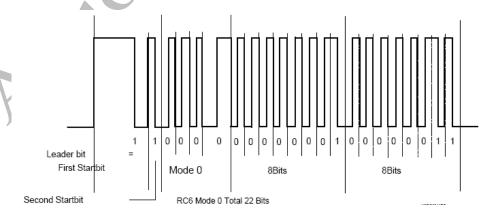

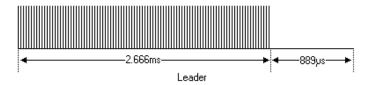

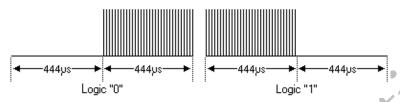

|    | 10.2        | .4   | RC6 Protocol ·····                                      | 113      |

| 1  | 0.3         | Regi | ister List ·····                                        | /<br>114 |

|    |             | _    | ister Description · · · · · · · · · · · · · · · · · · · |          |

| 1  | 0.4<br>10.4 | _    | IRC CTL                                                 |          |

|    | 10.4        |      | IRC STAT ·····                                          |          |

|    | 10.4        |      | _                                                       |          |

|    | 10.4        |      | IRC_CC IRC_KDC                                          | 116      |

|    | 10.4        |      | IPC WV                                                  | 117      |

|    | 10.4        |      | IRC_RCC                                                 | 117      |

|    | 10.4        |      | IRC FILTER                                              | 118      |

|    |             |      | _                                                       |          |

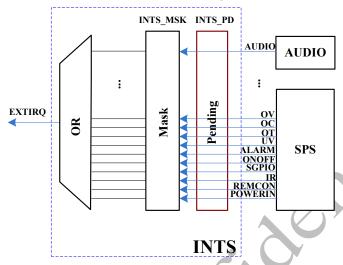

| 11 | Inte        | erru | pt Controller ·····1                                    | 18       |

| 1  | 1.1         | Feat | ures                                                    | 118      |

| 1  | 1.2         | D1   | 1 Pierra                                                | 110      |

| 1  | 1.2         |      | ck Diagram ·····                                        |          |

| 1  | 1.3         | Regi | ister List ·····                                        | 119      |

| 1  | 1.4         | Regi | ister Description                                       | 119      |

|    | 11.4.       | .1   | INTS_PD                                                 | 119      |

|    | 11.4.       | .2   | INTS_MSK ····                                           | 120      |

|    |             |      |                                                         |          |

| 12 | Gen         | iera | l Purpose I/O · · · · · · 1                             | .20      |

| 1  | 2.1         | Feat | ures····                                                | 120      |

| 1  | 2.2         | Regi | isters List                                             | 120      |

| 1  | 2.3         | Regi | ister Description · · · · · · · · · · · · · · · · · · · | 121      |

|    | 12.3.       | _    | MFP CTL                                                 |          |

|    | 12.3        | .2   | GPIO OUTEN                                              |          |

|    | 12.3        | .3   | GPIO_INEN····                                           | 122      |

|    | 12.3        | .4   | GPIO_DAT ····                                           | 122      |

|    | 12.3        | .5   | PAD_DRV ····                                            | 123      |

|    | 12.3        | .6   | PAD_EN ····                                             | 124      |

|    |             |      |                                                         |          |

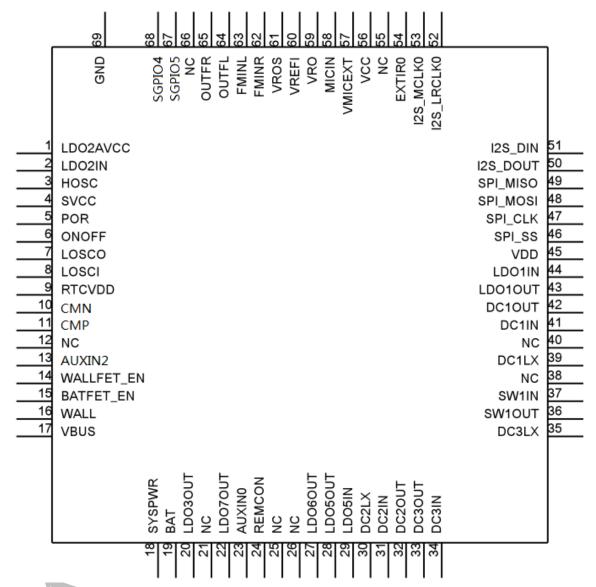

| 13 | Pin         | Des  | cription ····· 1                                        | .25      |

| 1  | 3.1         | ATC  | 22603C Pin Assignment                                   | 125      |

| 13.2   | ATC2603C Pin Definition                 | 125 |

|--------|-----------------------------------------|-----|

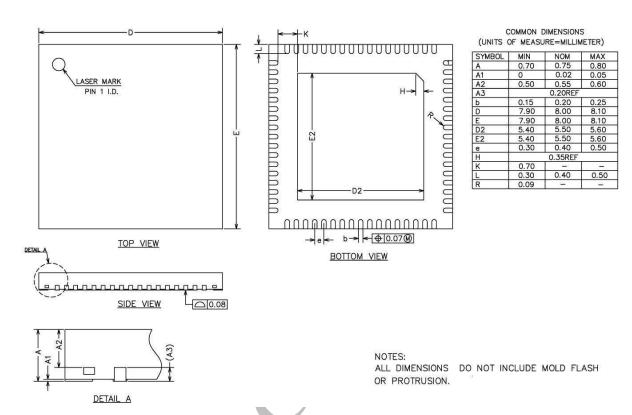

| 14 Pac | ckage and Ordering Information ······ 1 | 29  |

| 14.1   | Package Drawing····                     | 129 |

| Append | dix · · · · · · · · 1                   | 30  |

Actions Confidential

## **Revision History**

| Date                                                                                                                                   | Date Revision Description         |                                                       |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| 2014-08-30                                                                                                                             | 1.0                               | First Release                                         |  |  |  |  |  |  |

| 2015-03-10                                                                                                                             | 1.1                               | Correct some mistakes and add descriptions on ICMADC. |  |  |  |  |  |  |

| 2015-06-03 1.2 Correct mistakes on LDO11 & LDO12 functions descriptions.                                                               |                                   |                                                       |  |  |  |  |  |  |

| 2015-06-25                                                                                                                             | 2.0                               | Add electrical parameters tables and figures in Chap4 |  |  |  |  |  |  |

| 2015-07-30                                                                                                                             | 2.1 1. Correct mistakes of pin68; |                                                       |  |  |  |  |  |  |

| 2013-07-30                                                                                                                             |                                   | 2. Update parameters and registers.                   |  |  |  |  |  |  |

| 2015-09-23                                                                                                                             | 2.2                               | Correct conflicts in LDO parameters                   |  |  |  |  |  |  |

| 2015-06-25 2.0 Add electrical parameters tables and figures in Chap4 1. Correct mistakes of pin68; 2. Update parameters and registers. |                                   |                                                       |  |  |  |  |  |  |

Page 1

### Introduction

#### 1.1 Overview

ATC2603C is an integrated power management and audio subsystem which provides a cost effective, single-chip solution for portable multimedia systems. All the information from Master is configured through TWI (Two Wire Interface) interface of ATC2603C.

The integrated audio Codec provides all the necessary functions for high-quality recording and playback. Programmable on-chip amplifiers allow direct connection of headphones and microphones with a minimum of external components.

ATC2603C includes three programmable DC-DC converters, eight low-dropout (LDO) regulators and one current limit switch to generate suitable supply voltage for the system, including on-chip audio CODEC as well as off-chip components such as a digital core and memory chips. Each of these is voltage programmable. ATC2603C can be powered by a lithium battery, wall adaptor or USB.

An on-chip battery charger supports both trickle charging and fast (Constant Current, Constant Voltage) charging of single-cell Lithium battery. The charging current, termination voltage, and time-out are programmable to fit different types of batteries.

Internal power management circuit controls the start-up and shutdown sequence of supply voltages, as well as sleep and wake-up. It also detects and handles abnormal conditions such as overvoltage, overcurrent, etc.

A 32.768 kHz crystal oscillator should be supplied to ATC2603C system to get an accuracy clock for real time clock (RTC) and get alarm function for waking up the system. The master clock can be input directly from Master. IR and multi-channel ADC capable of waking up the system are also integrated.

## 1.2

#### **Audio CODEC**

Version 2.2

- 2.0 channel DAC, SNR (A-WEIGHTING) > 98dB, THD < -80dB

- 2.0 channel ADC, SNR(A-WEIGHTING) > 91dB, THD < -82dB

- Stereo 20mW PA (Power Amplifier) for headphone with 41 level volume control(volume update with zero-cross detection), traditional mode and direct drive mode, both with anti-pop circuit

- DAC supports sample rate of 192k/176.4k/96k/48k/32k/24k/16k/12k/8k/88.2k/44.1k/ 22.05k/11.025k

- ADC supports sample rate of 96k/48k/32k/24k/16k/12k/8k/44.1k/22.5k/11.025k

- Configurable high-pass filter with ADC

- Slave mode I2S, TDM mode only, Tx and Rx both

- 2.0 channel I2S Receiver and 2.0 channel transmitter

• I2S supports sample rate of 192k/176.4k/96k/48k/32k/24k/16k/12k/8k/88.2k/44.1k/22.05k/11.025k

#### **Power Supply Generation**

#### 3 DC-DCs

- DC-DC Buck Converter (0.7~1.4V, Up to 1200mA)

- DC-DC Buck Converter (1.3~2.2V, Up to 1000mA)

- DC-DC Buck Converter (2.6~3.3V, Up to 1000mA, when working without inductance, up to 800mA)

#### **8LDOs and 1 SWITCH:**

- LDO voltage regulators (2.6~3.3V, Up to 200mA), high PSRR(LDO1)

- LDO voltage regulators (2.6~3.3V, Up to 200mA), high PSRR(LDO2)

- LDO voltage regulator (1.5~2.0V, Up to 250mA) (LDO3)

- LDO voltage regulators (2.6~3.3V, Up to 150mA), high PSRR(LDO5)

- LDO voltage regulator (0.7~1.4V, Up to 200mA), high PSRR(LDO6)

- LDO voltage regulator (1.5~2.0V, Up to 200mA), high PSRR(LDO7)

- LDO voltage regulator (1.5~2.0V, Up to 5mA), for SVCC use(LDO11)

- LDO voltage regulator (2.6~3.3V, Up to 25mA), for RTCVDD use(LDO12)

- One SWITCH, configurable to LDO mode

- Overvoltage, Overcurrent, Overtemperature protection of DC-DCs and LDOs

#### **Battery Charger**

- Single-cell Lithium battery charger

- Thermal protection for charging control;

#### Power saving mode

- Several power saving modes including standby mode, sleep mode and deep-sleep mode

- "Always on" RTC with wake-up alarm

- In deep-sleep with RTC always on, the current of IBAT can be less than 30μA

#### **System Control**

- TWI slave Interface

- Handles power sequencing, power-on reset signal, sleep mode signal and interrupt signals

- Adaptive Power Distribute System, autonomous power source selection (Battery, Wall adaptor or USB bus)

#### Additional Features

- A multi-channel 10-bit ADC, can be used as voltage, current measurement or wake-up sources for Remote control

- An EXTIRQ to Master

- Configurable GPIO pins

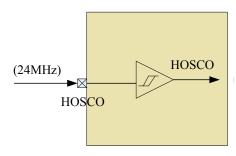

- 24MHz system clock input supported

- ESD Level of HBM pass over 2000V of all IOs

- QFN68 package, 8mm\*8mm, 0.4mm pin pitch

## 1.3 Typical Applications

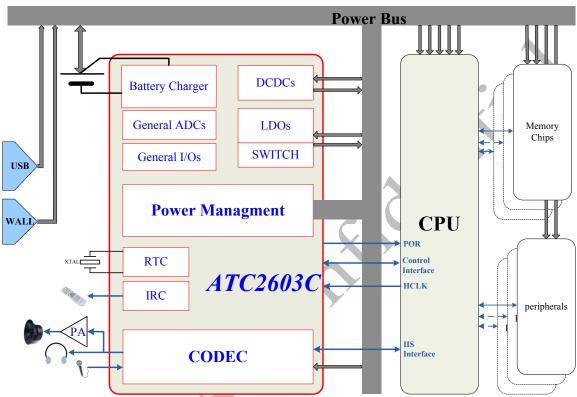

ATC2603C mainly consists of Power Management Unit and Audio CODEC block targeted at multimedia platform application. Figure 1-1 below shows the typical application diagram of ATC2603C.

Figure 1-1 Typical Application diagram

## 1.4 Ordering Information

Table 1-1 Ordering Information

| Part Numbers | Package | Size    |

|--------------|---------|---------|

| ATC2603C     | QFN68   | 8mm*8mm |

# 2 Absolute Maximum Rating

These absolute maximum ratings are stress ratings, operating at or beyond these ratings for more than 1ms may result in permanent damage. Unless otherwise noted, all voltage values are relative to VSS.

Table 2-1 Max ratings of ATC2603C

| Parameter           | Symbol                     | Min  | Max  | Unit |

|---------------------|----------------------------|------|------|------|

| Ambient Temperature | Tamb                       | TBD  | TBD  | °C   |

| Storage Temperature | Tstg                       | -55  | +150 | °C   |

| Supply Voltage      | DCxIN/WALL/VBUS/BAT/SYSPWR | -0.5 | +6.5 | V    |

| Imput Valtage       | Digital IO                 | -0.3 | 3.6  | V    |

| Input Voltage       | Analog IO (FMIN/MICIN)     | -0.3 | 3.6  | V    |

| ESD Stress Voltage  | VESD (Human Body Model)    | 2000 | -    | V    |

# 3 Recommended Operating Conditions

Table 3-1 Recommended Operating Voltage

| Parameter                 | Symbol                  | Min  | Тур | Max  | Unit |

|---------------------------|-------------------------|------|-----|------|------|

| Wall adapter input source | WALL                    | 4.3  | -   | 5.5  | V    |

| USB VBUS input source     | VBUS                    | 4.75 | -   | 5.25 | V    |

| Battery input source      | BAT                     | 3.0  | -   | 4.2  | V    |

| Supply voltage            | DCxVIN/LDOxIN/SWxIN     | 3.0  | -   | 5.5  | V    |

| Core supply               | VDD                     | -    | 1.8 | -    | V    |

| IO supply                 | VCC                     | -    | 3.1 | -    | V    |

| Ground                    | GND/AGND/DCxGND/CDPGNDx | -    | 0   | -    | V    |

Note: in DCxVIN/LDOxIN/SWxIN and DCxGND/CDPGNDx, x is number, for example, DC1VIN represents the Input Voltage of DC-DC1.

## 4 Electrical Characteristics

#### 4.1 Overshoot

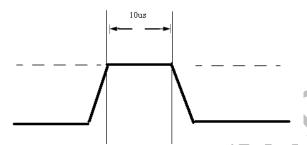

The maximum DC voltage on power supply pins is 6.5V. However, during voltage domains switching period, the device can tolerate overshoot for up to 10µs, as shown in Figure 4-1 below.

Figure 4-1 Tolerance for overshoot for up to 10us

Table 4-1 Extreme Values for Input Pins

| Parameter      | Symbol              | Start | Max | Unit |

|----------------|---------------------|-------|-----|------|

| Supply voltage | DCxIN/WALL/VBUS/BAT | -0.3  | 12  | V    |

ATC2603C can tolerate 1,000 times of such pulses. But exposed to overshoot circumstances for too many times may affect device's lifetime.

## 4.2 Powerpath

Table 4-2 Powerpath Parameters

| Symbol                 | Characteristic & Condition        | Min  | Тур                    | Max  | Units |

|------------------------|-----------------------------------|------|------------------------|------|-------|

| $V_{\mathrm{BUS}}$     | Bus input voltage Range           | 4.5  | 5                      | 5.5  | V     |

| $V_{WALL}$             | Wall input voltage Range          | 4.5  | 5                      | 5.5  | V     |

| $V_{BAT}$              | Bat input voltage Range           | 3.3  | 4.2                    | 4.4  | V     |

| V <sub>out(BUS)</sub>  | System Power Output Voltage       |      | V <sub>BUS</sub> -0.1  | 5    | V     |

| V <sub>out(WALL)</sub> | System Power Output Voltage       |      | V <sub>WALL</sub> -0.1 | 5    | V     |

| V <sub>out(BAT)</sub>  | System Power Output Voltage       |      | V <sub>BAT</sub> -0.1  | 4.3  | V     |

| R <sub>BUS(on)</sub>   | Internal Ideal Resistance         |      | 450                    |      | mΩ    |

| R <sub>WALL(on)</sub>  | Internal Ideal Resistance         |      | 300                    |      | mΩ    |

| R <sub>BAT(on)</sub>   | Internal Ideal Resistance         |      | 300                    |      | mΩ    |

| V <sub>WK(BUS)</sub>   | Wake Up Voltage                   | 4.05 | 4.2                    | 4.5  | V     |

| V <sub>WK(WALL)</sub>  | Wake Up Voltage                   | 4.05 | 4.2                    | 4.5  | V     |

| V <sub>UV(BAT)</sub>   | Under Voltage Int Threshold       | 3.1  | 3.3                    | 3.5  | V     |

| V <sub>OV(BAT)</sub>   | Over Voltage Int Threshold        | 4.3  | 4.4                    | 4.8  | V     |

| I <sub>OC(BAT)</sub>   | Over Current Protection Threshold | 600  | 1000                   | 1200 | mA    |

Copyright<sup>©</sup> 2014-2015 Actions (Zhuhai) Technology Co., Ltd. All rights reserved.

| V <sub>UV(BUS)</sub>     | Under Voltage Int Threshold       | 3.8 | 4.3  | 4.5  | V  |

|--------------------------|-----------------------------------|-----|------|------|----|

| $V_{OV(BUS)}$            | Over Voltage Int Threshold        | 5.5 | 6.3  | 6.8  | V  |

| $I_{OC(BUS)}$            | Over Current Protection Threshold | 600 | 1000 | 1200 | mA |

| V <sub>UV(WALL)</sub>    | Under Voltage Int Threshold       | 3.8 | 4.5  | 4.5  | V  |

| V <sub>OV(WALL)</sub>    | Over Voltage Int Threshold        | 5.5 | 6.3  | 6.8  | V  |

| I <sub>OC(WALL)</sub>    | Over Current Protection Threshold | 600 | 1000 | 1200 | mA |

| I <sub>LIMIT(BUS)</sub>  | Bus Input Current Limited         | 300 | 500  | 1000 | mA |

| I <sub>LIMIT(WALL)</sub> | Wall Input Current Limited        | 300 | 500  | 2000 | mA |

| V <sub>LIMIT(BUS)</sub>  | Bus Input Voltage Limited         | 4.2 | 4.3  | 4.5  | V  |

| $V_{\text{LIMIT(WALL)}}$ | Wall Input Voltage Limited        | 4.2 | 4.3  | 4.5  | V  |

## **4.3 DCDC**

Table 4-3 DCDC1 Parameters

| $V_{LIMIT(WALL)}$                    | Wall Input Voltage Limited              | 4.2  | 4.3     | 4.5 | V     |  |  |  |

|--------------------------------------|-----------------------------------------|------|---------|-----|-------|--|--|--|

| 4.3 DCDC  Table 4-3 DCDC1 Parameters |                                         |      |         |     |       |  |  |  |

| Symbol                               | Characteristic & Condition              | Min  | Тур     | Max | Units |  |  |  |

| Vi                                   | Input Voltage                           | 3.2  | )-      | 5   | V     |  |  |  |

| Vo                                   | Output Voltage                          | 0.7  | 1.0     | 1.4 | V     |  |  |  |

| Io                                   | Output Current Drivability △Vo/Vo=-5%   |      | 1200    |     | mA    |  |  |  |

| Fsw                                  | Switching Frequency                     | 0.85 | 1.6     | 2.7 | MHz   |  |  |  |

| Visionala                            | Output Ripple Voltage Vo=1.0V,Io=1000mA |      | 10      |     | mV    |  |  |  |

| Vripple                              | Output Ripple Voltage Vo=1.0V,Io=20mA   |      | 60      |     | T m v |  |  |  |

| Eff                                  | Efficiency Vi=3.8V Vo=1.0V,Io=400mA     |      | 85      |     | %     |  |  |  |

| Tpu                                  | Power Up Time                           | 15   | 20      | 30  | us    |  |  |  |

| Tpd                                  | Power Down Time Io=10mA                 |      | 5       |     | ms    |  |  |  |

| LNR                                  | Line Regulation Vi=3.3V-5.0V,Io=1000mA  |      | 0.05    |     | %/V   |  |  |  |

| LDR                                  | Load Regulation Vi=5V,Io=10mA-1000mA    |      | 0.05    |     | %/A   |  |  |  |

| LDTR                                 | Load Transient Response                 |      | 30      |     | mV    |  |  |  |

| LDIK                                 | Vi=5.0V,lo=10mA-1000mA,1us              |      | 30      |     | 111 V |  |  |  |

| Iocp                                 | Over Current Limit For Output           |      | 1800    |     | mA    |  |  |  |

| Vuvp                                 | Under Voltage Int For Output            |      | 0.9*Vo  |     | V     |  |  |  |

| Vovp                                 | Over Voltage Int For Output             |      | 1.1* Vo |     | V     |  |  |  |

| R(P)                                 | Power Mosfet Switches High-side         |      | 250     |     | mΩ    |  |  |  |

| L                                    | External Inductance DCR<50mΩ            |      | 2.2     |     | uН    |  |  |  |

| C                                    | External Capacitance ESR<50mΩ           |      | 10      |     | uF    |  |  |  |

Table 4-4 DCDC2 Parameters

| Symbol | Characteristic & Condition            | Min  | Тур  | Max  | Units |

|--------|---------------------------------------|------|------|------|-------|

| Vi     | Input Voltage                         | 3.2  | 4.1  | 5    | V     |

| Vo     | Output Voltage                        | 1.0  | 1.4  | 1.85 | V     |

| Io     | Output Current Drivability ΔVo/Vo=-5% |      | 1000 |      | mA    |

| Fsw    | Switching Frequency                   | 0.85 | 1.6  | 2.7  | MHz   |

Copyright<sup>©</sup> 2014-2015 Actions (Zhuhai) Technology Co., Ltd. All rights reserved.

|         |                                         | ,  |        |     |       |

|---------|-----------------------------------------|----|--------|-----|-------|

| Vripple | Output Ripple Voltage Vo=1.4V,Io=1000mA |    | 10     |     | mV    |

| vrippie | Output Ripple Voltage Vo=1.4V,Io=20mA   |    | 70     |     | 111 V |

| Eff     | Efficiency Vi=3.8V Vo=1.4V,Io=300mA     |    | 89     |     | %     |

| Tpu     | Power Up Time                           | 20 | 30     | 60  | us    |

| Tpd     | Power Down Time Io=10mA                 |    | 5      |     | ms    |

| LNR     | Line Regulation Vi=3.3V-5.0V,Io=1000mA  |    | 0.05   |     | %/V   |

| LDR     | Load Regulation Vi=5.0V,Io=10mA-1000mA  |    | 0.05   |     | %/A   |

| LDTR    | Load Transient Response                 |    | 40     |     | mV    |

| LDIK    | Vi=5.0V,Io=10mA-1000mA,1us              |    | 40     |     | III V |

| Iocp    | Over Current Limit For Output           |    | 1700   |     | mA    |

| Vuvp    | Under Voltage Int For Output            |    | 0.9*Vo |     | V     |

| Vovp    | Over Voltage Int For Output             |    | 1.1*Vo | 7.( | V     |

| Rds(on) | Power Mosfet Switches High-side         |    | 240    |     | mΩ    |

| L       | External Inductance DCR<50mΩ            |    | 4.7    |     | uН    |

| С       | External Capacitance ESR<50mΩ           |    | 10     | 7   | uF    |

Table 4-5 DCDC3 Parameters

| Symbol    | Characteristic & Condition                                | Min  | Тур    | Max | Units |

|-----------|-----------------------------------------------------------|------|--------|-----|-------|

| Vi        | Input Voltage                                             | 3.2  | 4.1    | 5   | V     |

| Vo        | Output Voltage                                            | 2.6  | 3.1    | 3.3 | V     |

| Io        | Output Current Drivability \( \Delta \text{Vo/Vo=-5\%} \) |      | 1000   |     | mA    |

| Fsw       | Switching Frequency                                       | 0.85 | 1.6    | 2.7 | MHz   |

| Virginals | Output Ripple Voltage Vo=3.1V,Io=1000mA                   |      | 10     |     | mV    |

| Vripple   | Output Ripple Voltage Vo=3.1V,Io=20mA                     |      | 100    |     | IIIV  |

| Eff       | Efficiency Vi=3.8V Vo=3.1V,Io=300mA                       |      | 92     |     | %     |

| Tpu       | Power Up Time                                             | 30   | 50     | 120 | us    |

| Tpd       | Power Down Time Io=10mA                                   |      | 5      |     | ms    |

| LNR       | Line Regulation Vi=3.3V-5.0V,Io=1000mA                    |      | 0.05   |     | %/V   |

| LDR       | Load Regulation Vi=5.0V,Io=10mA-1000mA                    |      | 0.05   |     | %/A   |

| LDTR      | Load Transient Response Vi=5.0V,Io=10mA-1000mA,1us        |      | 120    |     | mV    |

| Iocp      | Over Current Limit For Output                             |      | 1950   |     | mA    |

| Vuvp      | Under Voltage Int For Output                              |      | 0.9*Vo |     | V     |

| Vovp      | Over Voltage Int For Output                               |      | 1.1*Vo |     | V     |

| Rds(on)   | Power Mosfet Switches High-side                           |      | 270    |     | mΩ    |

| L         | External Inductance DCR<50mΩ                              |      | 2.2    |     | uН    |

| С         | External Capacitance ESR<50mΩ                             |      | 10     |     | uF    |

## 4.4 LDO

Table 4-6 LDO1 Parameters

Copyright<sup>©</sup> 2014-2015 Actions (Zhuhai) Technology Co., Ltd. All rights reserved.

| Symbol                 | Characteristic & Condition                           | Min | Тур  | Max  | Units |

|------------------------|------------------------------------------------------|-----|------|------|-------|

| Vi                     | Input Voltage                                        | 3.2 |      | 5    | V     |

| Vo                     | Output Voltage                                       | 2.6 | 3.1  | 3.3  | V     |

| Io                     | Output Current Drivability ΔVo/Vo=-5%                |     | 200  |      | mA    |

| PSRR                   | Power Supply Restrain Ratio Vi =3.6V, Io=200mA 10kHz |     | -38  |      | db    |

| Tpu                    | Power Up Time                                        | 600 | 800  | 1000 | us    |

| Tpd                    | Power Down Time Io=10mA                              |     | 2    |      | ms    |

| LNR                    | Line Regulation Vi=3.3V-5.0V,Io=400mA                |     | 0.05 |      | %/V   |

| LDR                    | Load Regulation Vi=5.0V,Io=10mA-400mA                |     | 0.05 |      | %/A   |

| LDTD                   | Load Transient Response                              |     | 75   |      | ····V |

| LDTR                   | Vi=5.0V,Io=10mA-400mA,1us                            |     | 75   |      | mV    |

| Iocp                   | Over Current Protect For Output                      |     | 900  |      | mA    |

| Vuvp                   | Under Voltage Protect For Output                     |     | 2.65 |      | V     |

| Vovp                   | Over Voltage Protect For Output Vo=3.1V              |     | 3.3  |      | V     |

| V <sub>drop(min)</sub> | Min Dropout voltage Io=400mA                         |     | 200  |      | mV    |

| С                      | External Capacitance ESR<100mΩ                       |     | 2.2  |      | uF    |

### Table 4-7 LDO2 Parameters

| Symbol          | Characteristic & Condition                           | Min | Тур  | Max  | Units |

|-----------------|------------------------------------------------------|-----|------|------|-------|

| Vi              | Input Voltage                                        | 3.2 |      | 5    | V     |

| Vo              | Output Voltage                                       | 2.6 | 3.1  | 3.3  | V     |

| Io              | Output Current Drivability ΔVo/Vo=-5%                |     | 200  |      | mA    |

| PSRR            | Power Supply Restrain Ratio Vi =3.6V, Io=200mA 10kHz |     | -42  |      | db    |

| Tpu             | Power Up Time                                        | 600 | 800  | 1000 | us    |

| Tpd             | Power Down Time Io=10mA                              |     | 2    |      | ms    |

| LNR             | Line Regulation Vi=3.3V-5.0V,Io=200mA                |     | 0.05 |      | %/V   |

| LDR             | Load Regulation Vi=5.0V,Io=10mA-200mA                |     | 0.05 |      | %/A   |

| LDTR            | Load Transient Response Vi=5.0V,Io=10mA-200mA,1us    |     | 50   |      | mV    |

| Iocp            | Over Current Protect For Output                      |     | 480  |      | mA    |

| Vuvp            | Under Voltage Protect For Output                     |     | 2.65 |      | V     |

| Vovp            | Over Voltage Protect For Output Vo=3.1V              |     | 3.35 |      | V     |

| $V_{drop(min)}$ | Min Dropout voltage Io=200mA                         |     | 350  |      | mV    |

| С               | External Capacitance ESR<100mΩ                       |     | 2.2  |      | uF    |

#### Table 4-8 LDO3 Parameters

| Symbol | Characteristic & Condition                                | Min | Тур | Max  | Units |

|--------|-----------------------------------------------------------|-----|-----|------|-------|

| Vi     | Input Voltage                                             | 3.2 |     | 5    | V     |

| Vo     | Output Voltage                                            | 1.5 | 1.8 | 2.0  | V     |

| Io     | Output Current Drivability \( \Delta \text{Vo/Vo=-5\%} \) |     | 200 |      | mA    |

| PSRR   | Power Supply Restrain Ratio Vi =3.6V, Io=200mA 10kHz      |     | -42 |      | db    |

| Tpu    | Power Up Time                                             | 600 | 800 | 1000 | us    |

| Tpd             | Power Down Time Io=10mA                              | 1    | ms  |

|-----------------|------------------------------------------------------|------|-----|

| LNR             | Line Regulation Vi=3.3V-5.0V,Io=200mA                | 0.05 | %/V |

| LDR             | Load Regulation Vi=5.0V,Io=10mA-200mA                | 0.05 | %/A |

| LDTR            | Load Transient Response<br>Vi=5.0V,Io=10mA-200mA,1us | 65   | mV  |

| Iocp            | Over Current Protect For Output                      | 725  | mA  |

| Vuvp            | Under Voltage Protect For Output                     | 1.65 | V   |

| Vovp            | Over Voltage Protect For Output Vo=1.8V              | 1.95 | V   |

| $V_{drop(min)}$ | Min Dropout voltage Io=200mA                         | 350  | mV  |

| С               | External Capacitance ESR<100mΩ                       | 1.0  | uF  |

#### Table 4-9 LDO5 Parameters

| Symbol                 | Characteristic & Condition                           | Min | Тур  | Max  | Units |

|------------------------|------------------------------------------------------|-----|------|------|-------|

| Vi                     | Input Voltage                                        | 3.2 |      | 5    | V     |

| Vo                     | Output Voltage                                       | 2.6 | 2.8  | 3.3  | V     |

| Io                     | Output Current Drivability ΔVo/Vo=-5%                |     | 150  |      | mA    |

| PSRR                   | Power Supply Restrain Ratio Vi =3.6V, Io=200mA 10kHz |     | -48  |      | db    |

| Tpu                    | Power Up Time                                        | 600 | 750  | 1000 | us    |

| Tpd                    | Power Down Time Io=10mA                              |     | 1    |      | ms    |

| LNR                    | Line Regulation Vi=3.3V-5.0V,Io=150mA                |     | 0.05 |      | %/V   |

| LDR                    | Load Regulation Vi=5.0V,Io=10mA-150mA                |     | 0.05 |      | %/A   |

| LDTR                   | Load Transient Response<br>Vi=5.0V,Io=10mA-150mA,lus |     | 30   |      | mV    |

| Iocp                   | Over Current Protect For Output                      |     | 380  |      | mA    |

| Vuvp                   | Under Voltage Protect For Output                     |     | 2.5  |      | V     |

| Vovp                   | Over Voltage Protect For Output Vo=2.8V              |     | 3.0  |      | V     |

| V <sub>drop(min)</sub> | Min Dropout voltage Io=100mA                         |     | 350  |      | mV    |

| С                      | External Capacitance ESR<100mΩ                       |     | 1.0  |      | uF    |

#### Table 4-10 LDO6 Parameters

| Symbol | Characteristic & Condition                           | Min | Тур  | Max | Units |

|--------|------------------------------------------------------|-----|------|-----|-------|

| Vi     | Input Voltage                                        | 3.2 |      | 5   | V     |

| Vo     | Output Voltage                                       | 0.7 | 1.2  | 1.4 | V     |

| Io     | Output Current Drivability \( \Delta Vo/Vo=-5\% \)   |     | 200  |     | mA    |

| PSRR   | Power Supply Restrain Ratio Vi =3.6V, Io=200mA 10kHz |     | -44  |     | db    |

| Tpu    | Power Up Time                                        | 400 | 550  | 700 | us    |

| Tpd    | Power Down Time Io=10mA                              |     | 1    |     | ms    |

| LNR    | Line Regulation Vi=3.3V-5.0V,Io=200mA                |     | 0.05 |     | %/V   |

| LDR    | Load Regulation Vi=5.0V,Io=10mA-200mA                |     | 0.05 |     | %/A   |

| LDTR   | Load Transient Response<br>Vi=5.0V,Io=10mA-200mA,1us |     | 35   |     | mV    |

| Iocp   | Over Current Protect For Output                      |     | 510  |     | mA    |

| Vuvp            | Under Voltage Protect For Output        | 1.0 | V  |

|-----------------|-----------------------------------------|-----|----|

| Vovp            | Over Voltage Protect For Output Vo=1.2V | 1.3 | V  |

| $V_{drop(min)}$ | Min Dropout voltage Io=200mA            | 350 | mV |

| С               | External Capacitance ESR<100mΩ          | 1.0 | uF |

#### Table 4-11 LDO7 Parameters

| Symbol          | Characteristic & Condition                           | Min | Тур  | Max | Units |

|-----------------|------------------------------------------------------|-----|------|-----|-------|

| Vi              | Input Voltage                                        | 3.2 |      | 5   | V     |

| Vo              | Output Voltage                                       | 1.5 | 1.8  | 2   | V     |

| Io              | Output Current Drivability ΔVo/Vo=-5%                |     | 200  |     | mA    |

| PSRR            | Power Supply Restrain Ratio Vi =3.6V, Io=200mA 10kHz |     | -44  |     | db    |

| Tpu             | Power Up Time                                        | 400 | 500  | 600 | us    |

| Tpd             | Power Down Time Io=10mA                              |     | 1    |     | ms    |

| LNR             | Line Regulation Vi=3.3V-5.0V,Io=200mA                |     | 0.05 |     | %/V   |

| LDR             | Load Regulation Vi=5.0V,Io=10mA-200mA                |     | 0.05 |     | %/A   |

| LDTR            | Load Transient Response Vi=5.0V,Io=10mA-200mA,1us    | V   | 35   |     | mV    |

| Iocp            | Over Current Protect For Output                      |     | 510  |     | mA    |

| Vuvp            | Under Voltage Protect For Output                     |     | 1.5  |     | V     |

| Vovp            | Over Voltage Protect For Output Vo=1.8V              |     | 1.9  |     | V     |

| $V_{drop(min)}$ | Min Dropout voltage Io=200mA                         |     | 350  |     | mV    |

| С               | External Capacitance ESR<100mΩ                       |     | 1.0  |     | uF    |

#### Table 4-12 LDO11 Parameters

| Symbol                 | Characteristic & Condition                                | Min | Тур  | Max | Units |

|------------------------|-----------------------------------------------------------|-----|------|-----|-------|

| Vi                     | Input Voltage                                             | 3.2 |      | 5   | V     |

| Vo                     | Output Voltage                                            | 2.6 | 3.1  | 3.3 | V     |

| Io                     | Output Current Drivability \( \Delta \text{Vo/Vo=-5\%} \) |     | 30   |     | mA    |

| Tpu                    | Power Up Time                                             |     | 5    |     | ms    |

| Tpd                    | Power Down Time Io=10mA                                   |     | 1    |     | ms    |

| LNR                    | Line Regulation Vi=3.3V-5.0V,Io=30mA                      |     | 0.05 |     | %/V   |

| LDR                    | Load Regulation Vi=5.0V,Io=1mA-30mA                       |     | 0.05 |     | %/A   |

| LDTR                   | Load Transient Response<br>Vi=5.0V, Io=1mA-30mA, 1us      |     | 80   |     | mV    |

| V <sub>drop(min)</sub> | Min Dropout voltage Io=20mA                               |     | 350  |     | mV    |

| С                      | External Capacitance ESR<100mΩ                            |     | 1.0  |     | uF    |

#### Table 4-13 LDO12 Parameters

| Symbol | Characteristic & Condition            |     | Тур | Max | Units |

|--------|---------------------------------------|-----|-----|-----|-------|

| Vi     | Input Voltage                         | 3.2 |     | 5   | V     |

| Vo     | Output Voltage                        |     | 1.8 |     | V     |

| Io     | Output Current Drivability ΔVo/Vo=-5% |     | 15  |     | mA    |

Copyright<sup>©</sup> 2014-2015 Actions (Zhuhai) Technology Co., Ltd. All rights reserved.

| Tpu             | Power Up Time                             | 100 | 180 | 250 | us   |

|-----------------|-------------------------------------------|-----|-----|-----|------|

| Tpd             | Power Down Time Io=5mA                    |     | 1   |     | ms   |

| LNR             | Line Regulation Vi=3.3V-5.0V,Io=15mA 0.05 |     |     |     | %/V  |

| LDR             | Load Regulation Vi=5.0V,Io=1mA-15mA       |     |     |     | %/A  |

| LDTR            | Load Transient Response                   |     | 30  |     | mV   |

|                 | Vi=5.0V,Io=1mA-15mA,1us                   |     | 30  |     | IIIV |

| $V_{drop(min)}$ | Min Dropout voltage Io=15mA               |     | 350 |     | mV   |

| С               | External Capacitance ESR<100mΩ            |     | 1.0 |     | uF   |

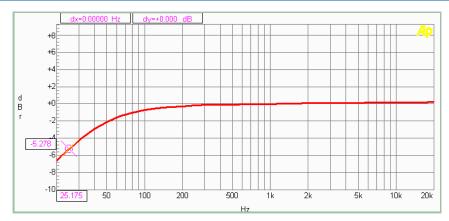

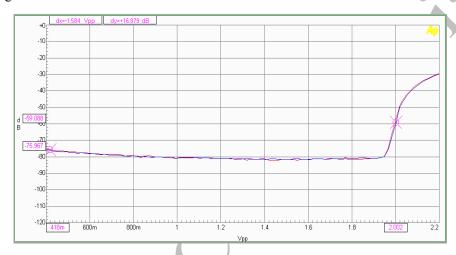

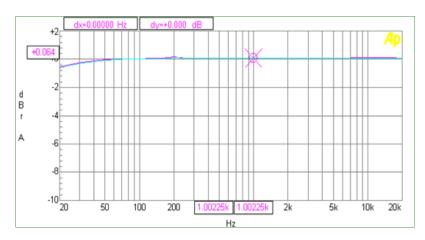

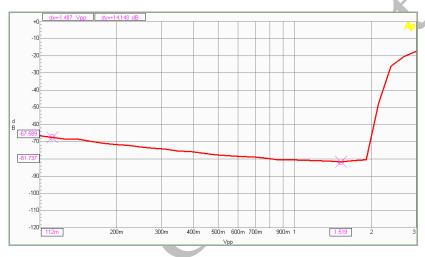

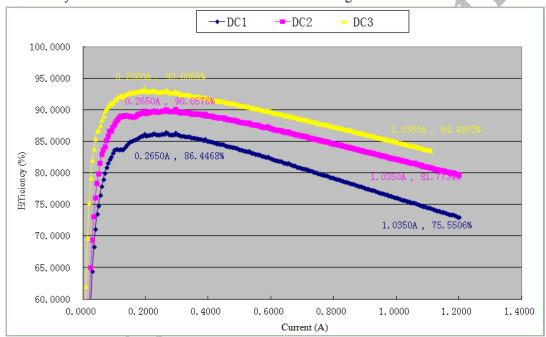

## 4.5 Typical Characteristics

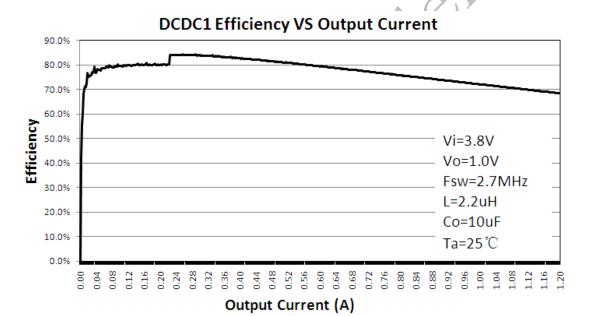

## 4.6 Efficiency Parameter

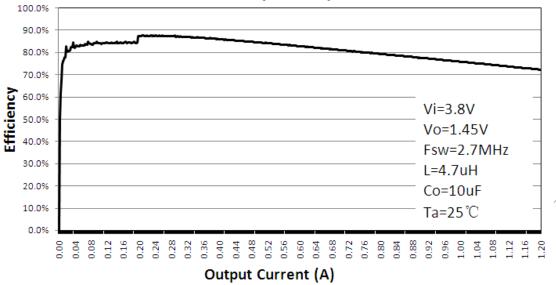

Figure 4-2 DCDC1 Efficiency

Figure 4-3 DCDC2 Efficiency

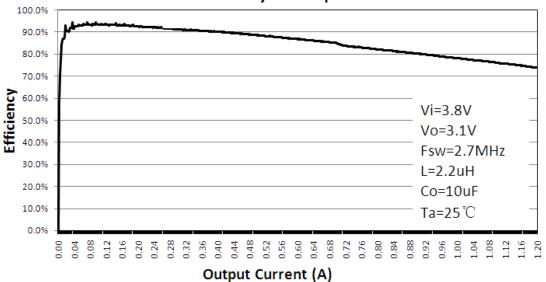

## **DCDC3 Efficiency VS Output Current**

Figure 4-4 DCDC3 Efficiency

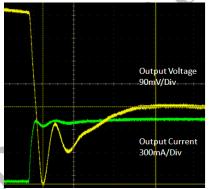

## 4.7 Load Transient Response

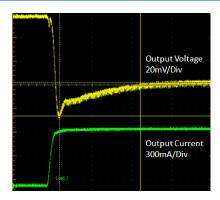

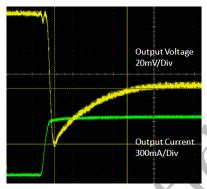

$\label{eq:Vi=3.8V} Vi=3.8V, Fsw=2.7MHz \ , \ 0-80\% load \ \ , \ \ Tr/Toff=1us \ , Co=10uF \ , \ Unless \ other \ Notes \ \ .$

Copyright<sup>©</sup> 2014-2015 Actions (Zhuhai) Technology Co., Ltd. All rights reserved.

Figure 4-5 DCDC1 Load Transient Response

Figure 4-6 DCDC2 Load Transient Response

Figure 4-7 DCDC3 Load Transient Response

## 5 Audio Codec Subsystem

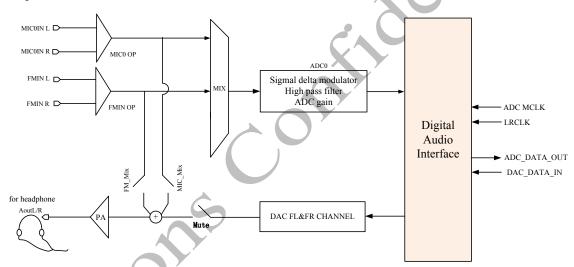

### 5.1 Audio Diagram

Audio Codec subsystem integrates I2S interface, DAC, ADC, AGC interface, MIC amplifier, FM amplifier and headphone PA. I2S interface in slave mode supports 2.0 channel transmitter and receiver. I2S supports sample rate of 192k/96k/48k/32k/24k/16k/12k/8k/88.2k/44.1k/22.05k/11.025k. The 2.0 channel Sigma-Delta DAC supports the same sample rate as I2S. The stereo 20mW PA (Power Amplifier) is integrated for headphone with 41-level volume and mute control, Non-direct and Direct Drive mode both with anti-pop circuit are supported for headphone. The subsystem supports stereo analog microphones (AMIC). The AMIC interface provides programmable bias output. There are configurable Automatic Gain Control (AGC), Zero Crossing and Noise gating for analog microphone.

Figure 5-1 Audio Diagram & Signal Path

## 5.1.1 Register List

Table 5-1 AUDIO OUT IN Controller Registers Address

| Name      | Physical Base Address |

|-----------|-----------------------|

| AUDIO_OUT | 0xA0                  |

| AUDIO_IN  | 0xA0                  |

Table 5-2 Audio Registers

|        |                | -                                     |

|--------|----------------|---------------------------------------|

| Offset | Register Name  | Description                           |

| 0x0    | AUDIOINOUT_CTL | AUDIO IN/OUT Control for I2S Register |

| 0x2    | DAC_DIGITALCTL | DAC Control EN&MUTE Register          |

| 0x3    | DAC_VOLUMECTL0 | DAC FL&FR VOLUME Control Register     |

| 0x4 | DAC_ANALOG0    | DAC Analog 0 Register                  |

|-----|----------------|----------------------------------------|

| 0x5 | DAC_ANALOG1    | DAC Analog 1 Register                  |

| 0x6 | DAC_ANALOG2    | DAC Analog 2 Register                  |

| 0x7 | DAC_ANALOG3    | DAC Analog 3 Register                  |

| 0x8 | ADC_DIGITALCTL | ADC0 Digital Control Register          |

| 0x9 | ADC_HPFCTL     | ADC0 High Pass Filter Control Register |

| 0xA | ADC_CTL        | ADC0 control register                  |

| 0xB | AGC_CTL0       | AGC0 Control 0 Register                |

| 0xC | AGC_CTL1       | AGC0 Control 1 Register                |

| 0xD | AGC_CTL2       | AGC0 Control 2 Register                |

| 0xE | ADC_ANALOG0    | ADC Analog 0 Register                  |

| 0xF | ADC_ANALOG1    | ADC Analog 1 Register                  |

#### **Register Description** 5.1.2

### 5.1.2.1 AUDIOINOUT\_CTL

| UXI                        | TIDC_I                                | ADC Allalog I Register                              |        |       |  |  |  |  |

|----------------------------|---------------------------------------|-----------------------------------------------------|--------|-------|--|--|--|--|

| 5.1.2 Register Description |                                       |                                                     |        |       |  |  |  |  |

| 5.1.2.1 AUDIOINOUT_CTL     |                                       |                                                     |        |       |  |  |  |  |

| ALIDIO IN                  | AUDIO IN/OUT Control for I2S Register |                                                     |        |       |  |  |  |  |

| Offset = $0x$              |                                       | ioi 125 Register                                    |        |       |  |  |  |  |

|                            |                                       | Description                                         | Aggess | Reset |  |  |  |  |

| Bit(s)                     | Name                                  | Description                                         | Access |       |  |  |  |  |

| 15:12                      | -                                     | Reserved                                            | -      | -     |  |  |  |  |

|                            | 1.000                                 | MCLK Divided to DAC                                 | DIV    |       |  |  |  |  |

| 11                         | MDD                                   | 0:DIV=1                                             | RW     | 0     |  |  |  |  |

|                            |                                       | 1:DIV=2                                             |        |       |  |  |  |  |

|                            |                                       | headset or earphone INOUT detect IRQ enable         |        |       |  |  |  |  |

| 10                         | HIOID                                 | 0: disable                                          | RW     | 0     |  |  |  |  |

|                            |                                       | 1: enable                                           |        |       |  |  |  |  |

|                            |                                       | Direct Drive Output Over Current status IRQ         |        |       |  |  |  |  |

|                            | • (                                   | 1: enable                                           |        |       |  |  |  |  |

|                            |                                       | 0: disable                                          |        |       |  |  |  |  |

| 9                          | OCIEN                                 | If DAC_ANALOG2[5] is enabled and                    | RW     | 0     |  |  |  |  |

|                            |                                       | DAC_ANALOG3[14] is high, when this bit is           |        |       |  |  |  |  |

|                            |                                       | enabled, an interrupt will be sent to the interrupt |        |       |  |  |  |  |

|                            | 7                                     | controller.                                         |        |       |  |  |  |  |

|                            |                                       | I2S Output Enable.                                  |        |       |  |  |  |  |

| 8                          | OEN                                   | 0: Disable                                          | RW     | 0     |  |  |  |  |

|                            |                                       | 1: Enable                                           |        |       |  |  |  |  |

| 7                          | -                                     | Reserved                                            | -      | -     |  |  |  |  |

|                            |                                       | I2S RX&TX Mode Select                               |        |       |  |  |  |  |

|                            |                                       | 00:3 wires mode                                     |        |       |  |  |  |  |

| 6:5                        | IMS                                   | 01:4 wires mode                                     | RW     | 00    |  |  |  |  |

|                            |                                       | 10:6 wires mode                                     |        |       |  |  |  |  |

|                            |                                       | 11:Reserved                                         |        |       |  |  |  |  |

| 4:0                        | -                                     | Reserved                                            | -      | -     |  |  |  |  |

|                            | •                                     |                                                     |        |       |  |  |  |  |

### 5.1.2.2 DAC\_DIGITALCTL

DAC Control EN\_MUTE Register

Offset = 0x02

| Bit(s)   | Name       | Description                      | Access | Reset |

|----------|------------|----------------------------------|--------|-------|

| 15:12    | -          | Reserved                         | RW     | 0     |

|          |            | DAC input source select          |        |       |

|          |            | 00:I2S0(music)                   |        |       |

| 11:10    | DACINSEL   | 01: Reserved                     | RW     | 00    |

|          |            | 10: Reserved                     |        | A     |

|          |            | 11: Reserved                     |        |       |

|          |            | DACFL&FR EN_DITH                 | . (    | ,     |

| 9        | DEDFL_FR   | 1:Enable                         | RW A   | 0     |

|          |            | 0:Disable                        |        |       |

|          |            | DAC INPUT SAMPLE RATE SEL        |        |       |

| 8        | DISRS      | 0:MCLK/256                       | RW     | 0     |

|          |            | 1:MCLK/128                       |        |       |

|          |            | DACFL&FR BANDWIDTH               |        |       |

|          |            | 00:Wide                          |        |       |

| 7:6      | DBWFL_FR   | 01:Middle                        | RW     | 00    |

|          |            | 10:Narrow                        |        |       |

|          |            | 11:Reserved                      |        |       |

|          |            | DAC FL&FR OUTPUT SAMPLE RATE SEL |        |       |

|          |            | 00:MCLK/16                       |        |       |

| 5:4      | DOSRSFL_FR | 01:MCLK/8                        | RW     | 00    |

|          |            | 10:MCLK/4                        |        |       |

|          |            | 11:MCLK/2                        |        |       |

|          |            | DACFR DIGITAL MUTE               |        |       |

| 3        | DMFR       | 1:Mute                           | RW     | 0     |

|          | •          | 0:Unmute                         |        |       |

|          | K          | DACFL DIGITAL MUTE               |        |       |

| 2        | DMFL       | 1:Mute                           | RW     | 0     |

|          |            | 0:Unmute                         |        |       |

|          |            | DACFR DIGITAL ENABLE             |        |       |

| 1        | DEFR       | 1:Enable                         | RW     | 0     |

| <b>Y</b> |            | 0:Disable                        |        |       |

|          |            | DACFL DIGITAL ENABLE             |        |       |

| 0        | DEFL       | 1:Enable                         | RW     | 0     |

|          |            | 0:Disable                        |        |       |

### 5.1.2.3 DAC\_VOLUMECTL0

DAC FL\_FR VOLUME CONTROL ((3/8) dB/level)

Offset = 0x03

| Bit(s) Name Description | Access | Reset |

|-------------------------|--------|-------|

|-------------------------|--------|-------|

|      |              | VOLUME CONTROL (3/8) dB/level  0xFF :+24 dB                                        |    |    |

|------|--------------|------------------------------------------------------------------------------------|----|----|

| 15:8 | DACFR_VOLUME | 0xBF: 0 dB<br>0xBE: -3/8 dB                                                        | RW | BE |

|      |              | 0x00 : -72 dB                                                                      |    |    |

| 7:0  | DACFL_VOLUME | VOLUME CONTROL (3/8) dB/level  0xFF:+24 dB  0xBF: 0 dB 0xBE: -3/8 dB  0x00: -72 dB | RW | BE |

## 5.1.2.4 DAC\_ANALOG0

DAC Analog Register

Offset = 0x04

| Bit(s) | Name    | Description                                                                                                                        | Access | Reset |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 15:14  | PAIB    | PA bias current control. 11:biggest 00:smallest                                                                                    | RW     | 01    |

| 13:12  | OPDAVB  | OPDA bias voltage control. 11:biggest 00:smallest                                                                                  | RW     | 01    |

| 11     | -       | Reserved                                                                                                                           | -      | -     |

| 10:8   | OPDAIB  | OPDA bias current control. 111:biggest 000:smallest                                                                                | RW     | 011   |

| 7:6    | OPDTSIB | OPDTS bias current control. 11:biggest 00:smallest                                                                                 | RW     | 01    |

| 5:4    | OPVBIB  | OPVB bias current control. 11:biggest 00:smallest                                                                                  | RW     | 01    |

| 3      | -       | Reserved                                                                                                                           | -      | -     |

| 3      | KFEN    | Karaoke Mix Function Enable 0:disable 1:enable Note: when enable this bit, MICOINL and MICOINR will be added and transmitted to PA | RW     | 0     |

| 2:0    | OPGIB   | OPG bias current control.                                                                                                          | RW     | 101   |

| 111:biggest  |  |

|--------------|--|

| 000:smallest |  |

### **5.1.2.5 DAC\_ANALOG1**

DAC Analog Register

Offset = 0x05

| Bit(s) | Name         | Description                                      | Access | Reset  |

|--------|--------------|--------------------------------------------------|--------|--------|

|        |              | MIC mute,                                        |        |        |

| 15     | MICMUTE      | 0: mute                                          | RW     | 0      |

|        |              | 1: Unmute                                        | A      |        |

|        |              | FM mute,                                         |        |        |

| 14     | FMMUTE       | 0: mute                                          | RW     | 0      |

|        |              | 1: Unmute                                        | X      |        |

| 13:11  | -            | Reserved                                         |        | -      |

|        |              | DACFL&FR Playback Mute                           |        |        |

| 10     | DACFL_FRMUTE | 0: mute DAC Playback,                            | RW     | 0      |

|        |              | 1: enable DAC playback                           |        |        |

|        |              | PA output stage IQ control.                      |        |        |

| 9:8    | 9:8 PAIQ     | 00:smallest                                      | RW     | 00     |

|        |              | 11:biggest                                       |        |        |

|        |              | Zero data for DAC analog part                    |        |        |

| 7      | ZERODT       | 0:disable,                                       | RW     | 0      |

|        |              | 1:enable                                         |        |        |

|        |              | PA output swing select.                          |        |        |

|        |              | 0:2.828Vpp                                       |        |        |

|        |              | 1:1.6Vpp                                         |        |        |

|        |              | This bit will control the attenuation before     |        |        |

|        |              | DAC's output goes into PA.                       |        |        |

| 6      | PASW         | Set this bit to 1 when PA is driving a           | RW     | 1      |

| O      | TAS W        | headphone, there must to be attenuation for      | ICVV   | 1      |

|        |              | DAC's output (from about 2.4Vpp to 1.6Vpp)       |        |        |

|        |              | and PA will output 1.6Vpp at max volume.         |        |        |

|        |              | Set it to 0, there will be no attenuation and PA |        |        |

| \      |              | will output 2.4Vpp and can function as           |        |        |

|        | <b>Y</b>     | LINEOUT.                                         |        |        |

|        |              | Headphone Amp Volume Control.                    |        |        |

|        |              | 41 levels in total                               |        |        |

| 5:0    | VOLUME       | (Values between 0b000000 and 0b101000 are        | RW     | 000000 |

| 5.0    | · JEGINE     | valid. Any value over 0b101000 set to it will be | 10,7   | 30000  |

|        |              | taken as 0b101000 actually. Reading value will   |        |        |

|        |              | just show what you have written to it.)          |        |        |

### **5.1.2.6 DAC\_ANALOG2**

DAC Analog2 Register

Copyright<sup>©</sup> 2014-2015 Actions (Zhuhai) Technology Co., Ltd. All rights reserved.

Offset = 0x06

| Bit(s) | Name       | Description                                         | Access   | Reset |

|--------|------------|-----------------------------------------------------|----------|-------|

|        |            | PA Output Volume Near Zero Detect:                  |          |       |

|        |            | 0:Invalid                                           |          |       |

| 1.5    | DA ZD      | 1:Valid                                             | DW       | 0     |

| 15     | PAZD       | When this bit is selected 1, "click" of volume      | RW       | 0     |

|        |            | tuning will cut down. But if small volume is        |          |       |

|        |            | selected, this bit should be 0 to avoid some issue. |          |       |

| 14:12  | -          | Reserved                                            | -        | -     |

|        |            | DAC Current select:                                 |          |       |

| 11     | DACI       | 0:Small                                             | RW       | 0     |

|        |            | 1:Large                                             | • 6      | ~     |

|        |            | PA bias Double for ATP2 mode:                       | V        |       |

| 10     | P2IB       | 0: *1                                               | RW       | 0     |

|        |            | 1: *2                                               |          |       |

|        |            | For ATP2,On-chip ramp Connect EN:                   | <b>Y</b> |       |

| 9      | ATP2CE     | 0: Disconnect                                       | RW       | 0     |

|        |            | 1: Connect                                          |          |       |

|        |            | Antipop2 PA discharge control:                      |          |       |

| 8      | PAVDC      | 0: switch open                                      | RW       | 0     |

|        |            | 1: switch closed, discharge                         |          |       |

|        |            | FML add FMR to PAL and PAR                          |          |       |