# **S500 Datasheet**

Version: 1.4

2015-07-17

# **Declaration**

#### Disclaimer

Information given in this document is provided just as a reference or example for the purpose of using Actions' products, and cannot be treated as a part of any quotation or contract for sale.

Actions products may contain design defects or errors known as anomalies or errata which may cause the products' functions to deviate from published specifications. Designers must not rely on the instructions of Actions' products marked "Reserved" or "undefined". Actions reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

ACTIONS DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL EXPRESS OR IMPLIED WARRANTIES OF MERCHANTABILITY, ACCURACY, SECURITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT OF INTELLECTUAL PROPERTY AND THE LIKE TO THE INFORMATON OF THIS DOCUMENT AND ACTIONS PRODUCTS.

IN NO EVENT SHALL ACTIONS BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES WHATSOEVER, INCLUDING, WITHOUT LIMITATION FOR LOST OF DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND ARISING FROM USING THE INFORMATON OF THIS DOCUMENT AND ACTIONS PRODUCTS. REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF ACTIONS OR OTHERS; STRICT LIABILITY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER ACTIONS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES OR NOT.

Actions' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Actions and further testing and/or modification will be fully at the risk of the customer.

### Ways of obtaining information

Copies of this document and/or other Actions product literature, as well as the Terms and Conditions of Sale Agreement, may be obtained by visiting Actions' website at: <a href="http://www.actions-semi.com">http://www.actions-semi.com</a> or from an authorized Actions representative.

#### **Trademarks**

The word "Actions" and the logo are the trademarks of Actions Semiconductor Co., Ltd, and Actions (Zhuhai) Technology Co., Limited is authorized to use them. Word "炬芯" is the trademark of Actions (Zhuhai) Technology Co., Limited. Names and brands of other companies and their products that may from time to time descriptively appear in this document are the trademarks of their respective holders, no affiliation, authorization, or endorsement by such persons are claimed or implied except as may be expressly stated therein.

### **Rights Reserved**

The provision of this document shall not be deemed to grant buyers any right in and to patent, copyright, trademark, trade secret, know how, and any other intellectual property of Actions or others.

#### Miscellaneous

Information contained or described herein relates only to the Actions products and as of the release date of this publication, abrogates and supersedes all previously published data and specifications relating to such products provided by Actions or by any other person purporting to distribute such information.

Actions reserves the rights to make changes to information described herein at any time without notice. Please contact your Actions sales representatives to obtain the latest information before placing your product order.

#### **Additional Support**

Additional product and company information can be obtained by visiting the Actions website at: <a href="http://www.actions-semi.com">http://www.actions-semi.com</a>

# **Contents Table**

| Co | ntents   | Table                                 | ·····i |

|----|----------|---------------------------------------|--------|

| Re | vision H | History ·····                         | xiii   |

| 1  | Intro    | oduction·····                         | 1      |

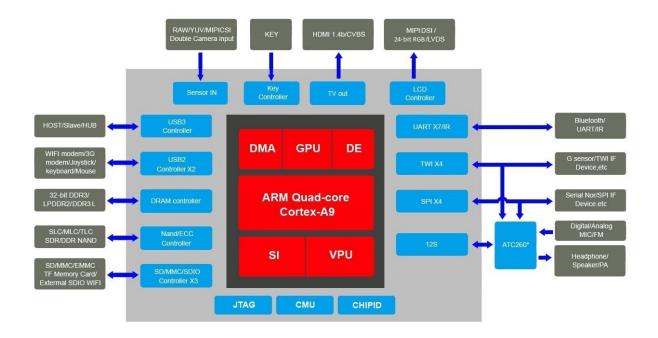

| _  | 1.1      | Overview                              |        |

|    | 1.2      | Features ·····                        | 1      |

|    | 1.2.1    |                                       |        |

|    | 1.2.2    | ·                                     |        |

|    | 1.2.3    |                                       |        |

|    | 1.2.4    |                                       |        |

|    | 1.2.5    |                                       |        |

|    | 1.2.6    |                                       |        |

|    | 1.2.7    | 7 System Components                   | 3      |

|    | 1.2.8    | · · · · · · · · · · · · · · · · · · · |        |

|    | 1.2.9    | External Memory ······                | 4      |

|    | 1.2.1    | LO Display Subsystem ·····            | 5      |

|    | 1.2.1    |                                       |        |

|    | 1.2.1    |                                       |        |

|    | 1.2.1    | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |        |

|    | 1.2.1    |                                       |        |

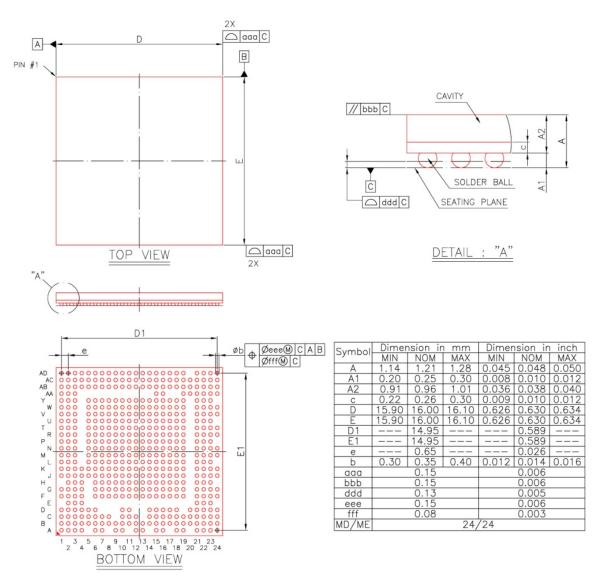

|    | 1.2.1    | L5 Package ·····                      | 9      |

|    | 1.3      | Application Diagram                   | 10     |

|    | 1.4      | Pin Description ·····                 | 10     |

|    | 1.4.1    | Pin Order List ·····                  | 10     |

|    | 1.4.2    |                                       |        |

|    | 1.4.3    | B Pin Multiplex List·····             | 45     |

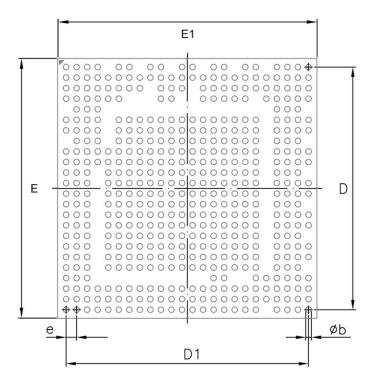

|    | 1.5      | Package ····                          |        |

|    | 1.5.1    |                                       |        |

|    | 1.5.2    | 2 Landing Pattern Recommendation      | 59     |

|    | 1.6      | Electrical Characteristics ······     | 60     |

|    | 1.6.1    |                                       |        |

|    | 1.6.2    |                                       |        |

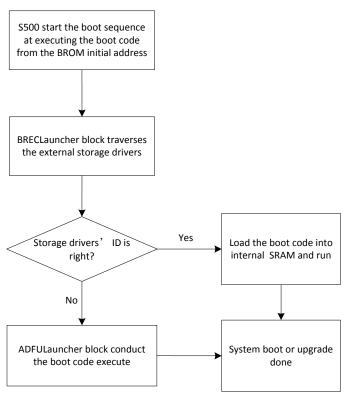

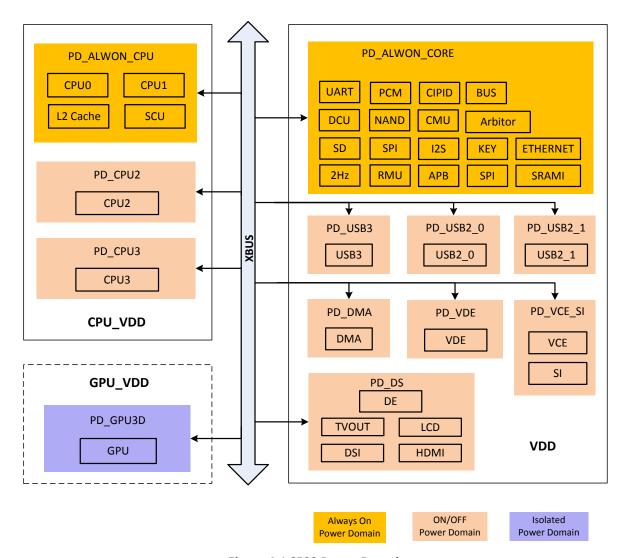

| 2  | Syste    | em Control·····                       | 63     |

| _  | -        | System Boot ·····                     |        |

|    | 2.1      | •                                     |        |

|    | 2.2      | Address Mapping                       |        |

|    | 2.3      | System Secure                         | 65     |

| 3  | Cloc     | k and Reset Management Unit ······    | 66     |

|    | 3.1      | Overview                              | 66     |

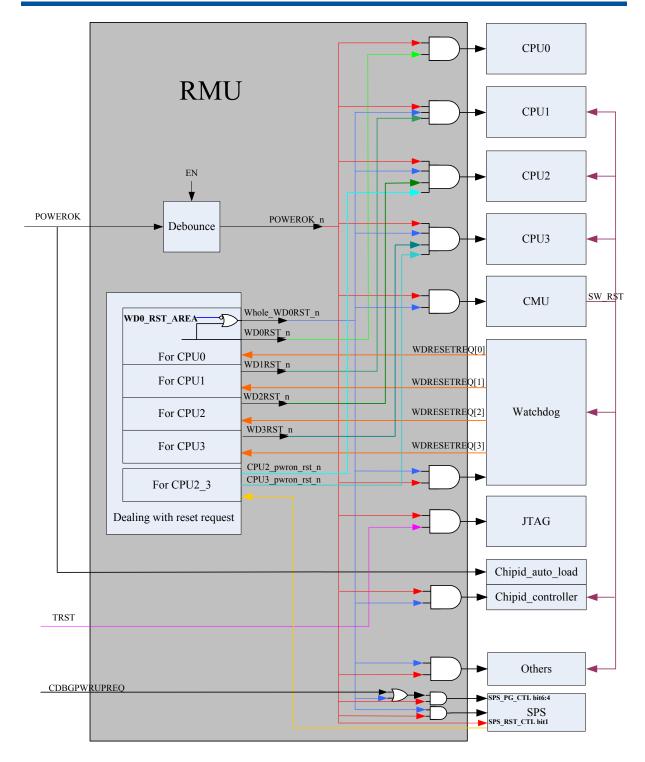

|    | 3.2      | RMU (Reset Management Unit)           | 66     |

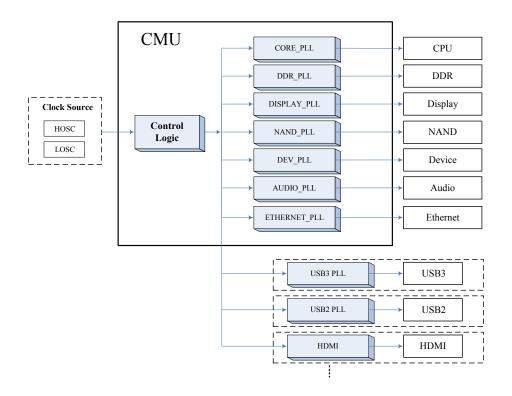

|   |                                                    | Clock Management Unit) ····· |                  |

|---|----------------------------------------------------|------------------------------|------------------|

|   |                                                    | ck Diagram ·····             |                  |

|   |                                                    | ister List·····              |                  |

|   |                                                    | ister Description            | 69               |

|   | 3.3.3.1                                            | CMU_SENSORCLK ·····          | ····· 69         |

|   | 3.3.3.2                                            | CMU_LCDCLK                   |                  |

|   | 3.3.3.3                                            | CMU_DSIPLL_CLK ·····         |                  |

|   | 3.3.3.4                                            | CMU_CSICLK                   |                  |

|   | 3.3.3.5                                            | CMU_DECLKCMU_SICLK           |                  |

|   | 3.3.3.6                                            | CMU_SICLK                    |                  |

|   | 3.3.3.7<br>3.3.3.8                                 | CMU_UART1CLK                 |                  |

|   | 3.3.3.9                                            | CMU_UART2CLK                 |                  |

|   | 3.3.3.10                                           | CMU PWM4CLK                  |                  |

|   | 3.3.3.11                                           | CMU PWM5CLK······            |                  |

|   | 3.3.3.12                                           | CMU PWMOCLK                  |                  |

|   | 3.3.3.13                                           | CMU PWM1CLK                  |                  |

|   | 3.3.3.14                                           | CMU PWM2CLK                  |                  |

|   | 3.3.3.15                                           | CMU PWM3CLK                  |                  |

|   | 3.3.3.16                                           | CMU DEVCLKENO                |                  |

|   | 3.3.3.17                                           | CMU DEVCLKEN1·····           |                  |

|   | 3.3.3.18                                           | CMU DEVRSTO                  |                  |

|   | 3.3.3.19                                           | CMU DEVRST1 ·····            |                  |

|   | 3.3.3.20                                           | CMU UART3CLK ······          |                  |

|   | 3.3.3.21                                           | CMU_UART4CLK ·····           |                  |

|   | 3.3.3.22                                           | CMU_UART5CLK ······          |                  |

|   | 3.3.3.23                                           | CMU_UART6CLK ······          |                  |

|   | 3.3.4 App                                          | lication Note ·····          | ····· <b>7</b> 9 |

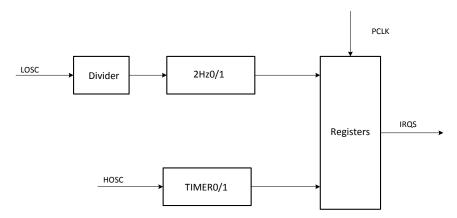

|   | 3.4 2Hz/Ti                                         | imer01 ·····                 | 79               |

|   |                                                    | ck diagram ·····             |                  |

|   |                                                    | ister List·····              |                  |

|   |                                                    | ister Description·····       |                  |

|   | 3.4.3.1                                            | TWOHZ0_CTL                   |                  |

|   | 3.4.3.2                                            | TO CTL                       |                  |

|   | 3.4.3.3                                            | T0 CMP                       | 81               |

|   | 3.4.3.4                                            | TO_VAL                       | 81               |

|   | 3.4.3.5                                            | T1_CTL                       | 81               |

|   | 3.4.3.6                                            | T1_CMP                       |                  |

|   | 3.4.3.7                                            | T1_VAL                       |                  |

|   | 3.4.3.8                                            | TwoHz1_CTL ·····             | 82               |

|   |                                                    |                              |                  |

| 4 | SPS (Smart                                         | Power System) ·····          | 83               |

|   | 4.1 Overvi                                         | ew                           | 83               |

|   | 4.2 Dlask (                                        | Diagram ·····                | 0.2              |

|   |                                                    | -                            |                  |

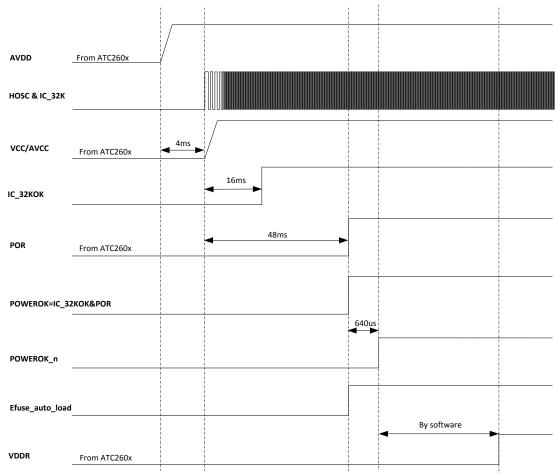

|   | 4.3 Power                                          | On Sequence                  | 85               |

|   | 4.4 Function                                       | on Description·····          | 85               |

|   |                                                    | er List ·····                |                  |

|   | 15 Dogicte                                         |                              |                  |

|   | •                                                  |                              |                  |

|   | 4.6 Registe                                        | er Description·····          | 86               |

|   | 4.6 Registe<br>4.6.1 SPS                           | er Description               | 86<br>86         |

|   | 4.6 Registe<br>4.6.1 SPS<br>4.6.2 SPS              | er Description               | 86<br>86         |

|   | 4.6 Registe<br>4.6.1 SPS<br>4.6.2 SPS<br>4.6.3 SPS | er Description               |                  |

| 5 | MPC            | ore Processor (ARM Cortex-A9R4) ······ | 90     |

|---|----------------|----------------------------------------|--------|

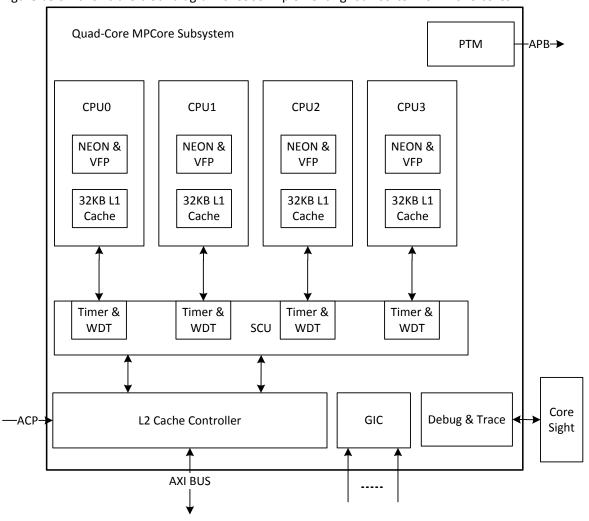

|   | 5.1            | Overview                               | 90     |

|   | 5.2            | Features ····                          | 90     |

|   | 5.3            | Block Diagram                          | ··· 91 |

|   | 5.4            | Function Description ·····             | 91     |

|   | 5.4.1          | Interfaces ·····                       | ··· 91 |

|   | 5.             | 4.1.1 AXI Interface ······             |        |

|   | 5.             | 4.1.2 PTM interface ······             |        |

|   | 5.4.2          |                                        |        |

|   | 5.4.3          | ,                                      |        |

|   | 5.4.4          |                                        |        |

|   | _              | 4.4.1 Overview·····                    |        |

|   |                | 4.4.2 Features                         |        |

|   | 5.             | 4.4.3 Application Notes ······         | 93     |

| 6 | DMA            | (Direct Memory Access) ·····           | ···94  |

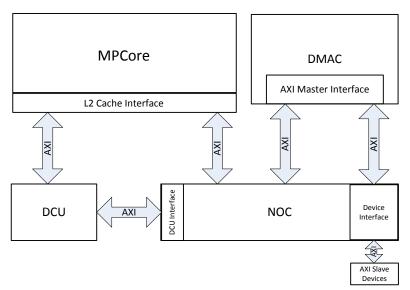

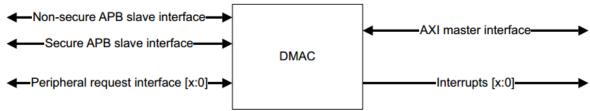

|   | 6.1            | Overview ····                          | 94     |

|   | 6.2            | Block Diagram ····                     | ··· 94 |

|   | 6.3            | Function Description                   | 94     |

|   | 6.4            | Register List                          | 96     |

|   | 6.5            | Register Description                   |        |

|   | 6.5.1          |                                        |        |

|   | 6.5.2          |                                        |        |

|   | 6.5.3          |                                        |        |

|   | 6.5.4          |                                        |        |

|   | 6.5.5          | _                                      |        |

|   | 6.5.6<br>6.5.7 | =                                      |        |

|   | 6.5.8          | <del>-</del>                           |        |

|   | 6.5.9          | <u> </u>                               |        |

|   | 6.5.1          | <u> </u>                               |        |

|   | 6.5.1          |                                        |        |

|   | 6.5.1          | <del>-</del> -                         |        |

|   | 6.5.1          |                                        |        |

|   | 6.5.1          | .4 DMAx_START ·····                    | 101    |

|   | 6.5.1          |                                        |        |

|   | 6.5.1          | <del>-</del>                           |        |

|   | 6.5.1          |                                        |        |

|   | 6.5.1          |                                        |        |

|   | 6.5.1          |                                        |        |

|   | 6.5.2          |                                        |        |

|   | 6.5.2          |                                        |        |

|   | 6.5.2          |                                        |        |

|   | 6.5.2          | 23 DMAx_CURRENT_DESTINATION_POINTER    |        |

|   | 6.6            |                                        |        |

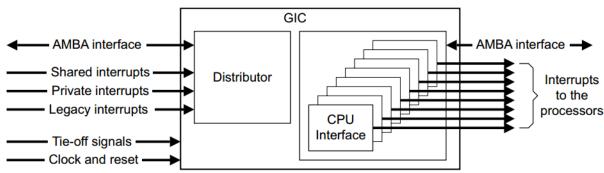

| 7 | GIC (          | General Interrupt Controller)          |        |

|   | 7.1            | Overview                               |        |

|   | 7.2            | Block Diagram ·····                    | · 105  |

|   | 7.3            | Function Description                   | · 105  |

|    | 7.3.1        |                                              |     |

|----|--------------|----------------------------------------------|-----|

|    | 7.3.2        | · · · · · · · · · · · · · · · · · · ·        |     |

|    | 7.3.3        |                                              |     |

|    | 7.3.4        | Lockable Shared Peripheral Interrupts (LSPI) | 108 |

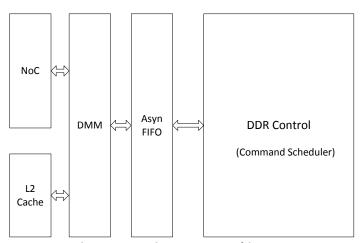

| 8  | DCU          | (DDR SDRAM Control Unit)                     | 109 |

|    | 8.1          | Overview                                     | 109 |

|    | 8.2          | Block Diagram ·····                          | 109 |

|    | 8.3          | Function Description ·····                   | 109 |

| 9  | SRAI         | VII (BROM and SRAM Interface Controller)     | 111 |

|    | 9.1          | Overview                                     | 111 |

|    | 9.2          | Timing Diagram                               | 111 |

|    | 9.3          | Register List                                | 111 |

|    | 9.4          | Register Description ·····                   |     |

|    | 9.4.1        | SRAMI_CTL                                    | 111 |

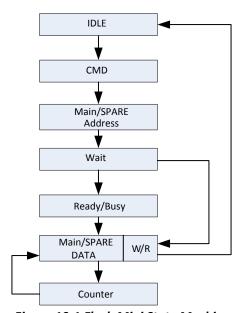

| 10 | ) NAN        | D Controller ·····                           | 112 |

|    | 10.1         | Overview ····                                | 112 |

|    | 10.2         | Function Description                         |     |

|    | 10.2         |                                              |     |

|    | 10.2         |                                              |     |

|    | 10.2         | .3 BCH Encoder/Decoder ······                | 113 |

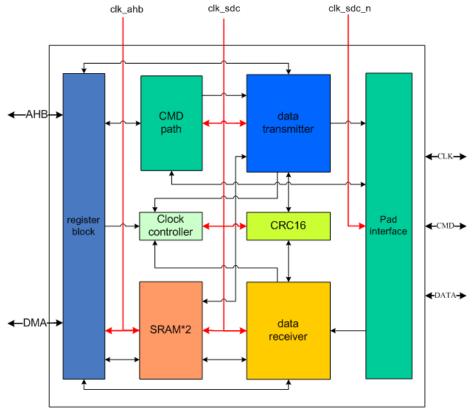

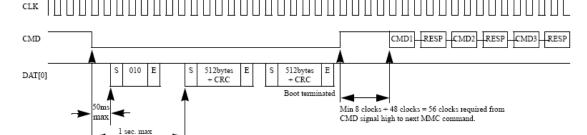

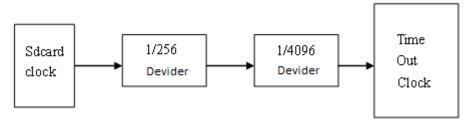

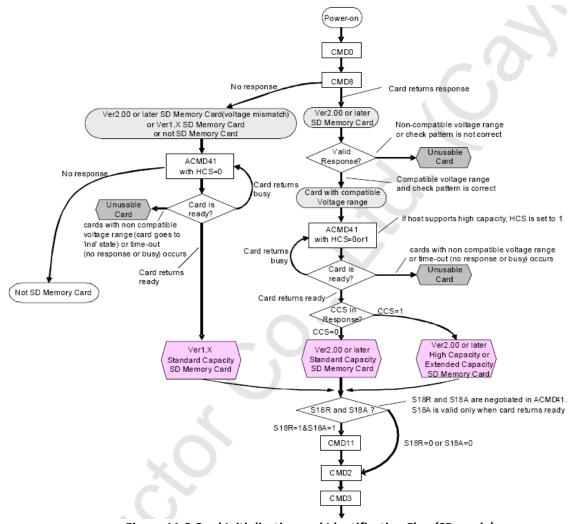

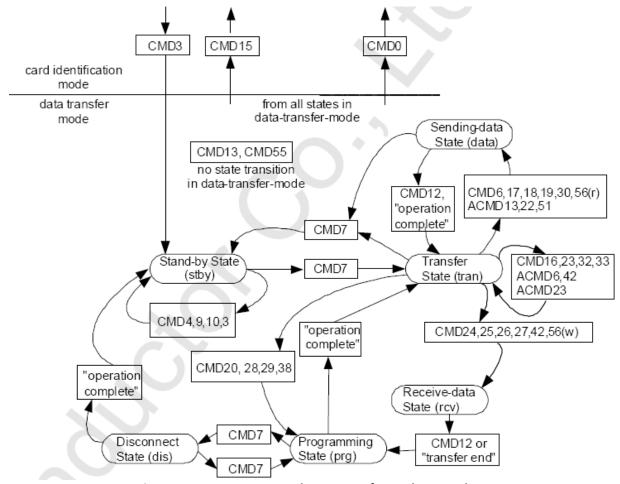

| 11 | L SDC        | (SD/MMC Controller)                          | 114 |

|    | 11.1         | Overview ·····                               |     |

|    | 11.2         | Block Diagram ·····                          | 114 |

|    | 11.3         | Function Description                         |     |

|    | 11.3         |                                              |     |

|    | 11.3         |                                              |     |

|    | 11.4         | Register List                                |     |

|    | 11.5         | Register Description ·····                   |     |

|    | 11.5         |                                              |     |

|    | 11.5         |                                              |     |

|    | 11.5         | <del>-</del>                                 |     |

|    | 11.5         |                                              |     |

|    | 11.5         | <del>-</del>                                 |     |

|    | 11.5<br>11.5 | =                                            |     |

|    | 11.5         | <del>-</del>                                 |     |

|    | 11.5         | <del>-</del>                                 |     |

|    | 11.5         | <del>-</del>                                 |     |

|    | 11.5         | =                                            |     |

|    | 11.5         | <del>-</del>                                 |     |

|    | 11.5         |                                              |     |

|    | 11.5         | <b>– –</b>                                   |     |

|    | 11.6         | Application Note ·····                       | 124 |

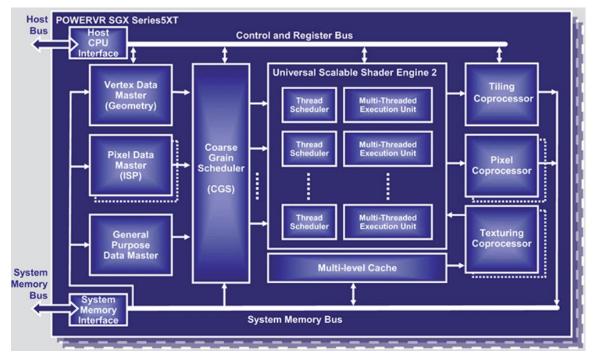

| 12 | 2 GPU        |                                              |     |

| 12.2 Block Diagram  12.3 Function Description  12.4 Register List  12.5 Register Description  12.6 Application Note  13 SI (CMOS Sensor Interface) |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 12.4 Register List                                                                                                                                 |     |

| 12.4 Register List                                                                                                                                 |     |

| 12.5 Register Description                                                                                                                          |     |

| 12.6 Application Note ·····                                                                                                                        |     |

|                                                                                                                                                    |     |

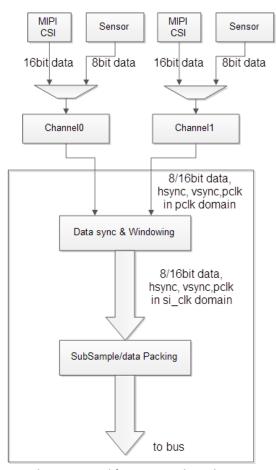

| 13 SI (CMOS Sensor Interface) ······                                                                                                               | 128 |

|                                                                                                                                                    | 128 |

| 13.1 Overview                                                                                                                                      | 128 |

|                                                                                                                                                    |     |

| -                                                                                                                                                  |     |

| 13.3 Function Description                                                                                                                          |     |

| 13.3.1 Data Synchronization ······                                                                                                                 |     |

| 13.3.2 Windowing ·····                                                                                                                             |     |

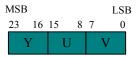

| 13.3.3 Storing format                                                                                                                              | 129 |

| 13.4 Register List ·····                                                                                                                           | 129 |

| 13.5 Register Description ······                                                                                                                   | 130 |

| 13.5.1 SI ENABLE······                                                                                                                             |     |

| 13.5.2 SI_INT_STAT                                                                                                                                 |     |

| 13.5.3 SI_CH0_CTRL······                                                                                                                           |     |

| 13.5.4 SI CHO ROW RANGE                                                                                                                            |     |

| 13.5.5 SI CHO COL RANGE                                                                                                                            |     |

| 13.5.6 SI CHO ADDRY                                                                                                                                |     |

| 13.5.7 SI CHO ADDRU                                                                                                                                |     |

| 13.5.8 SI CHO ADDRV                                                                                                                                |     |

| 13.5.9 SI CH1 CTRL                                                                                                                                 |     |

| 13.5.10 SI CH1 ROW RANGE                                                                                                                           |     |

| 13.5.11 SI CH1 COL RANGE······                                                                                                                     |     |

| 13.5.12 SI CH1 ADDRY                                                                                                                               |     |

| 13.5.13 SI CH1 ADDRU                                                                                                                               |     |

| 13.5.14 SI_CH1_ADDRV                                                                                                                               | 133 |

| 13.6 Application Note ······                                                                                                                       | 134 |

|                                                                                                                                                    |     |

| 14 MIPI CSI2                                                                                                                                       |     |

| 14.1 Overview ·····                                                                                                                                | 135 |

| 14.2 Function Description                                                                                                                          | 135 |

| 14.3 Register List ·····                                                                                                                           | 135 |

| 14.4 Register Description ·····                                                                                                                    | 136 |

| 14.4.1 CSI CTRL                                                                                                                                    |     |

| 14.4.2 SHORT PACKET······                                                                                                                          |     |

| 14.4.3 ERROR_PENDING······                                                                                                                         |     |

| 14.4.4 STATUS PENDING ······                                                                                                                       |     |

| 14.4.5 LANE_STATUS                                                                                                                                 |     |

| 14.4.6 CSI_PHY_TO                                                                                                                                  |     |

| 14.4.7 CSI_PHY_T1                                                                                                                                  |     |

| 14.4.8 CSI_PHY_T2                                                                                                                                  |     |

| 14.4.9 CSI_ANALOG_PHY······                                                                                                                        | 140 |

| 14.4.10 CSI_MAP                                                                                                                                    |     |

| 14.4.11 CONTEXTO_CFG ······                                                                                                                        |     |

| 14.4.12 CONTEXTO_STATUS ······                                                                                                                     | 142 |

|    | 14.4.13<br>14.4.14 |                       | CONTEXT1_CFG                 |     |

|----|--------------------|-----------------------|------------------------------|-----|

|    | 14.4               | .14                   | CONTEXT1_STATUS ·····        | 142 |

|    | 14.5               | Appl                  | cation Note ·····            | 143 |

| 15 | Vide               | o Co                  | ec                           | 144 |

|    | 15.1               | Over                  | /iew ·····                   | 144 |

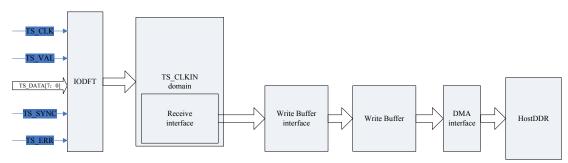

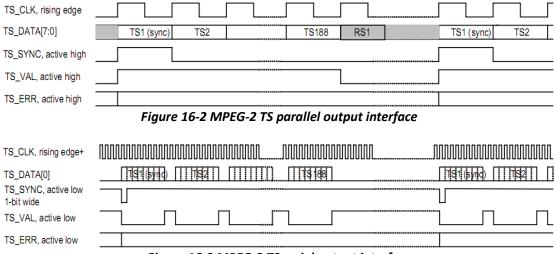

| 16 | TSIF               | (Tran                 | sport Stream Interface)····· | 146 |

|    | 16.1               | Over                  | /iew·····                    | 146 |

|    | 16.2               | Bloc                  | Diagram ·····                | 146 |

|    | 16.3               | Func                  | tion Description             | 146 |

|    | 16.3               | .1                    | Timing Specifications ······ | 146 |

|    | 16.4               | Regis                 | ter List ·····               | 147 |

|    | 16.5               | Regis                 | ter Description ·····        | 147 |

|    | 16.5               | .1                    | TS_CTRL ·····                |     |

|    | 16.5               | .2                    | TS_STATUS                    |     |

|    | 16.5               | .3                    | TS_RXDATA·····               | 148 |

|    | 16.6               | Appl                  | cation Note ·····            | 148 |

| 17 | LCDO               | (LCE                  | Controller)                  | 149 |

|    | 17.1               | •                     | ,<br>/iew                    |     |

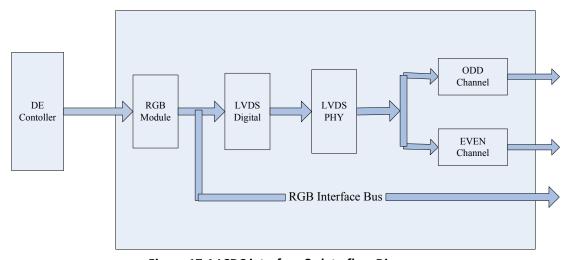

|    | 17.2               |                       | Diagram ·····                |     |

|    | 17.2               |                       | tion Description ······      |     |

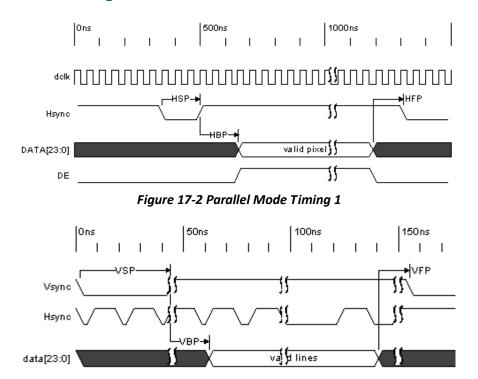

|    | 17.3               |                       | RGB LCD Interface ······     |     |

|    | _                  | . <u>.</u><br>7.3.1.: |                              |     |

|    |                    | 7.3.1.                | •                            |     |

|    |                    | 7.3.1.                | <u> </u>                     |     |

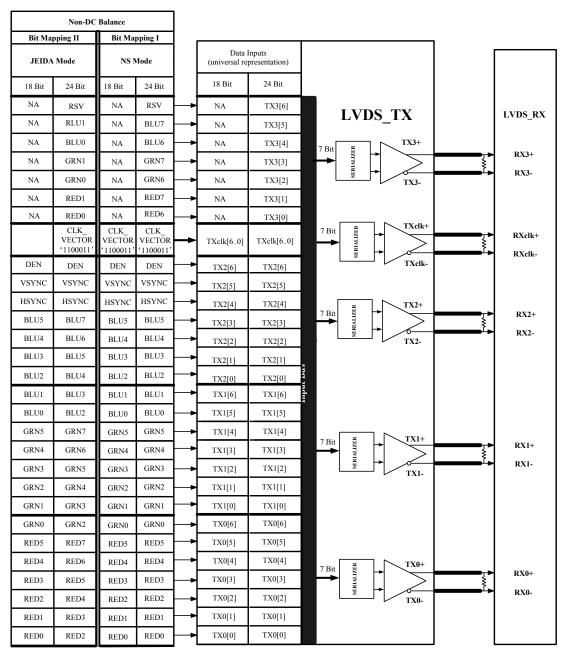

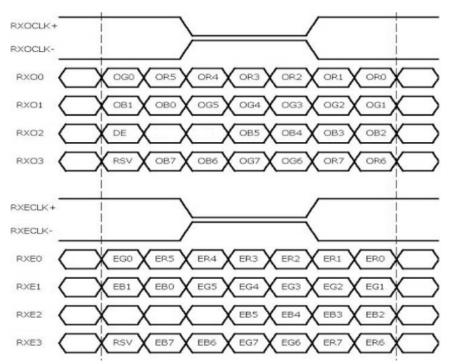

|    | 17.3               | .2                    | LVDS LCD Interface           |     |

|    | 17                 | 7.3.2.                |                              |     |

|    | 17.4               | Regis                 | ter List ·····               | 153 |

|    | 17.5               | Regis                 | ter Description ·····        | 154 |

|    | 17.5               | .1                    | LCD0_CTL ·····               | 154 |

|    | 17.5               | .2                    | LCD0_SIZE ·····              | 155 |

|    | 17.5               | .3                    | LCD0_STATUS ·····            |     |

|    | 17.5               | .4                    | LCD0_TIM0                    |     |

|    | 17.5               | .5                    | LCD0_TIM1 ·····              |     |

|    | 17.5               | .6                    | LCD0_TIM2 ·····              |     |

|    | 17.5               | .7                    | LCD0_COLOR·····              |     |

|    | 17.5               | .8                    | LCD0_IMG_XPOS ·····          |     |

|    | 17.5               | .9                    | LCD0_IMG_YPOS·····           |     |

|    | 17.5               |                       | LVDS_CTL                     |     |

|    | 17.5               |                       | LVDS_ALG_CTL0·····           |     |

|    | 17.6               | Appl                  | cation Note ·····            | 160 |

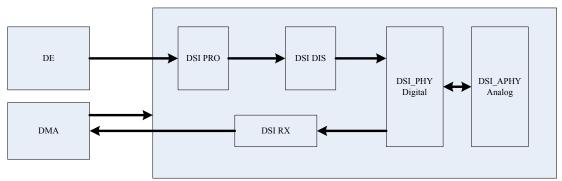

| 18 | МІРІ               |                       |                              |     |

|    | 18.1               | Over                  | view ·····                   | 161 |

|    | 18.2               | Bloc                  | Diagram ····                 | 161 |

|    | 18.3               | Func                  | cion Description ·····       | 161 |

| 18.5       Register Description         18.5.1       DSI_CTRL         18.5.2       DSI_SIZE         18.5.3       DSI_COLOR         18.5.4       DSI_VIDEO_CFG         18.5.5       DSI_RGBHTO         18.5.6       DSI_RGBHT1         18.5.7       DSI_RGBVTO         18.5.8       DSI_RGBVT1 |                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 18.5.1       DSI_CTRL         18.5.2       DSI_SIZE         18.5.3       DSI_COLOR         18.5.4       DSI_VIDEO_CFG         18.5.5       DSI_RGBHT0         18.5.6       DSI_RGBHT1         18.5.7       DSI_RGBVT0                                                                         |                   |

| 18.5.2 DSI_SIZE                                                                                                                                                                                                                                                                               |                   |

| 18.5.4 DSI_VIDEO_CFG                                                                                                                                                                                                                                                                          |                   |

| 18.5.5 DSI_RGBHT0                                                                                                                                                                                                                                                                             |                   |

| 18.5.6 DSI_RGBHT1                                                                                                                                                                                                                                                                             |                   |

| 18.5.7 DSI_RGBVT0                                                                                                                                                                                                                                                                             |                   |

|                                                                                                                                                                                                                                                                                               |                   |

| 18.5.8 DSI_RGBVT1                                                                                                                                                                                                                                                                             |                   |

|                                                                                                                                                                                                                                                                                               |                   |

| 18.5.9 DSI_TIMEOUT ·····                                                                                                                                                                                                                                                                      |                   |

| 18.5.10 DSI_TR_STA                                                                                                                                                                                                                                                                            | 168<br>169<br>169 |

| 18.5.11 DSI_INT_EN                                                                                                                                                                                                                                                                            | 169<br>169<br>169 |

| 18.5.12 DSI_ERROR_REPORT 18.5.13 DSI_FIFO_ODAT                                                                                                                                                                                                                                                | 169<br>169        |

| 18.5.14 DSI FIFO IDAT                                                                                                                                                                                                                                                                         | 169               |

| 18.5.15 DSI IPACK                                                                                                                                                                                                                                                                             |                   |

| 18.5.16 DSI_PACK_CFG                                                                                                                                                                                                                                                                          | 169               |

| 18.5.17 DSI PACK HEADER ····································                                                                                                                                                                                                                                  |                   |

| 18.5.18 DSI TX TRIGGER······                                                                                                                                                                                                                                                                  |                   |

| 18.5.19 DSI RX TRIGGER                                                                                                                                                                                                                                                                        |                   |

| 18.5.20 DSI_LANE_CTRL                                                                                                                                                                                                                                                                         | 171               |

| 18.5.21 DSI_LANE_STA ······                                                                                                                                                                                                                                                                   | 172               |

| 18.5.22 DSI_PHY_T0                                                                                                                                                                                                                                                                            |                   |

| 18.5.23 DSI_PHY_T1                                                                                                                                                                                                                                                                            |                   |

| 18.5.24 DSI_PHY_T2 ·····                                                                                                                                                                                                                                                                      |                   |

| 18.5.25 DSI_PIN_MAP                                                                                                                                                                                                                                                                           |                   |

| 18.5.26 DSI_PHY_CTRL                                                                                                                                                                                                                                                                          |                   |

| 18.6 Application Note                                                                                                                                                                                                                                                                         | 177               |

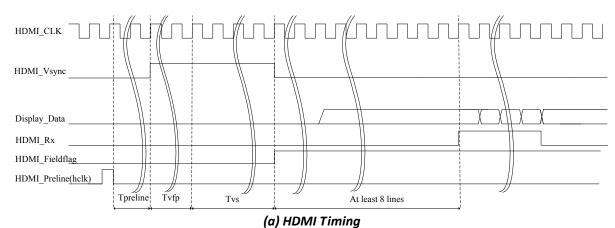

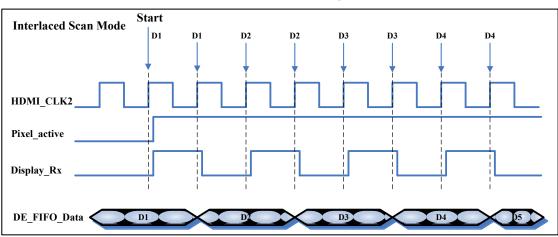

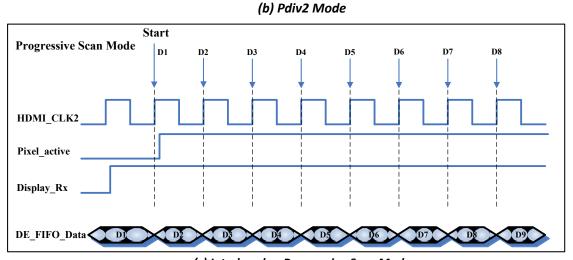

| 19 HDMI Interface ·····                                                                                                                                                                                                                                                                       | 178               |

| 19.1 Overview                                                                                                                                                                                                                                                                                 | 178               |

|                                                                                                                                                                                                                                                                                               |                   |

| 19.2 Function Description                                                                                                                                                                                                                                                                     |                   |

|                                                                                                                                                                                                                                                                                               |                   |

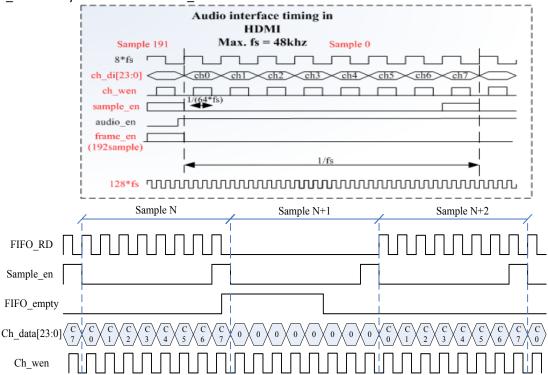

| 19.2.2 HDMI Audio Interface ······                                                                                                                                                                                                                                                            | 180               |

| 19.3 Application Note                                                                                                                                                                                                                                                                         | 180               |

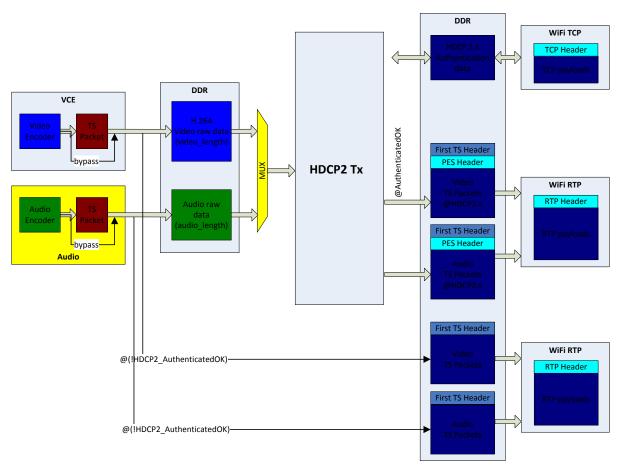

| 20 HDCP2 Tx                                                                                                                                                                                                                                                                                   | 181               |

| 20.1 Overview                                                                                                                                                                                                                                                                                 | 181               |

| 20.2 Block Diagram ·····                                                                                                                                                                                                                                                                      | 181               |

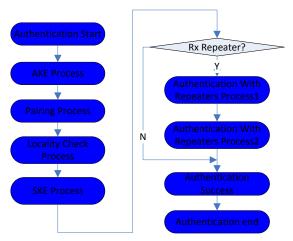

| 20.3 Function Description ·······                                                                                                                                                                                                                                                             |                   |

| ·                                                                                                                                                                                                                                                                                             |                   |

| 20.4 Register List ·····                                                                                                                                                                                                                                                                      |                   |

| 20.5 Application Note                                                                                                                                                                                                                                                                         | 183               |

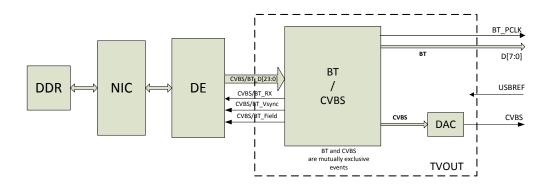

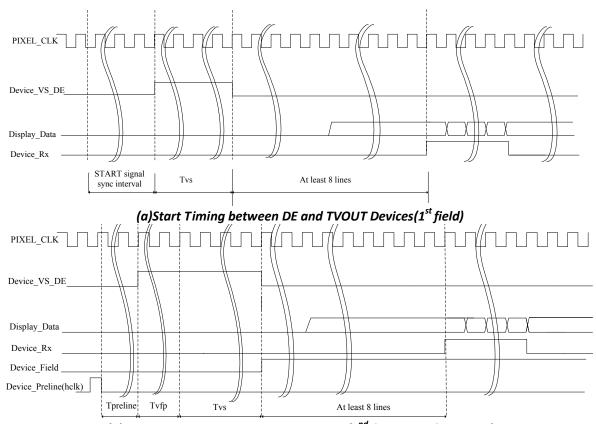

| 21 TVOUT                                                                                                                                                                                                                                                                                      | 184               |

| 21.1 Overview                                                                                                                                                                                                                                                                                 | 184               |

| 21.2 Block Diagram ·····                                                                                                                                                                                                                                                                      | 184               |

| •                                                                                                                                                                                                                                                                                             |                   |

| 21.3 Function Description ————————————————————————————————————                                                                                                                                                                                                                                |                   |

| :                          | 21.4                                                                                                                                        | Regis                                                                                 | ster List ·····                                                                                                                                                                                                                          | 185                                                                                                                 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| :                          | 21.5                                                                                                                                        | Regis                                                                                 | ster Description ·····                                                                                                                                                                                                                   | 186                                                                                                                 |

|                            | 21.5                                                                                                                                        | 5.1                                                                                   | TVOUT_EN                                                                                                                                                                                                                                 | 186                                                                                                                 |

|                            | 21.5                                                                                                                                        | 5.2                                                                                   | TVOUT_OCR                                                                                                                                                                                                                                |                                                                                                                     |

|                            | 21.5                                                                                                                                        | 5.3                                                                                   | TVOUT_STA·····                                                                                                                                                                                                                           |                                                                                                                     |

|                            | 21.5                                                                                                                                        | 5.4                                                                                   | TVOUT_CCR ·····                                                                                                                                                                                                                          |                                                                                                                     |

|                            | 21.5                                                                                                                                        | _                                                                                     | TVOUT_BCR                                                                                                                                                                                                                                |                                                                                                                     |

|                            | 21.5                                                                                                                                        | _                                                                                     | TVOUT_CSCR                                                                                                                                                                                                                               |                                                                                                                     |

|                            | 21.5<br>21.5                                                                                                                                |                                                                                       | TVOUT_PRL                                                                                                                                                                                                                                |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | CVBS_MSR ·····                                                                                                                                                                                                                           |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | CVBS_AL_SEPO ·······                                                                                                                                                                                                                     |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | CVBS_AL_SEPE                                                                                                                                                                                                                             |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | CVBS_AD_SEP                                                                                                                                                                                                                              |                                                                                                                     |

|                            | 21.5                                                                                                                                        | 5.13                                                                                  | CVBS_HUECR ·····                                                                                                                                                                                                                         |                                                                                                                     |

|                            | 21.5                                                                                                                                        | 5.14                                                                                  | CVBS_SCPCR ·····                                                                                                                                                                                                                         |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | CVBS_SCFCR·····                                                                                                                                                                                                                          |                                                                                                                     |

|                            | 21.5                                                                                                                                        | _                                                                                     | CVBS_CBACR·····                                                                                                                                                                                                                          |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | CVBS_SACR ·····                                                                                                                                                                                                                          |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | BT_MSR0                                                                                                                                                                                                                                  |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | BT_MSR1······BT_AL_SEPO·····                                                                                                                                                                                                             |                                                                                                                     |

|                            | 21.5<br>21.5                                                                                                                                |                                                                                       | BT_AL_SEPE                                                                                                                                                                                                                               |                                                                                                                     |

|                            | 21.5                                                                                                                                        |                                                                                       | BT_AP_SEP                                                                                                                                                                                                                                |                                                                                                                     |

|                            | 21.6                                                                                                                                        |                                                                                       | ication Note ······                                                                                                                                                                                                                      |                                                                                                                     |

|                            |                                                                                                                                             |                                                                                       |                                                                                                                                                                                                                                          |                                                                                                                     |

| 22                         | USB                                                                                                                                         | 3                                                                                     |                                                                                                                                                                                                                                          | 194                                                                                                                 |

|                            |                                                                                                                                             |                                                                                       |                                                                                                                                                                                                                                          |                                                                                                                     |

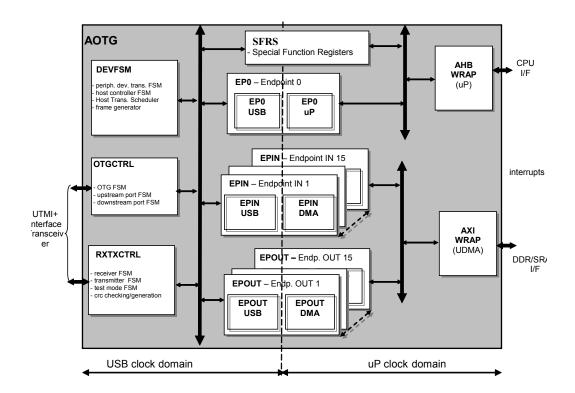

| 23                         | USB                                                                                                                                         | 2                                                                                     |                                                                                                                                                                                                                                          | 195                                                                                                                 |

|                            |                                                                                                                                             |                                                                                       |                                                                                                                                                                                                                                          |                                                                                                                     |

| :                          | 23.1                                                                                                                                        | Over                                                                                  | view ······                                                                                                                                                                                                                              | 195                                                                                                                 |

| :                          | 23.1<br>23.2                                                                                                                                | Over<br>Block                                                                         | view ····································                                                                                                                                                                                                | 195<br>195                                                                                                          |

| :                          | 23.1<br>23.2<br>23.3                                                                                                                        | Over<br>Block<br>Fund                                                                 | view  C Diagram ······ tion Description ·····                                                                                                                                                                                            | 195<br>195<br>196                                                                                                   |

| :                          | 23.1<br>23.2                                                                                                                                | Over<br>Block<br>Fund                                                                 | view ····································                                                                                                                                                                                                | 195<br>195<br>196                                                                                                   |

|                            | 23.1<br>23.2<br>23.3<br>23.4                                                                                                                | Over<br>Block<br>Func<br>Appl                                                         | view  C Diagram ······ tion Description ·····                                                                                                                                                                                            | 195<br>195<br>196<br>196                                                                                            |

| :<br>:<br>:<br>:           | 23.1<br>23.2<br>23.3<br>23.4                                                                                                                | Over<br>Block<br>Fund<br>Appl<br>lio In/                                              | view  k Diagram  tion Description  ication Note                                                                                                                                                                                          | 195<br>195<br>196<br>196                                                                                            |

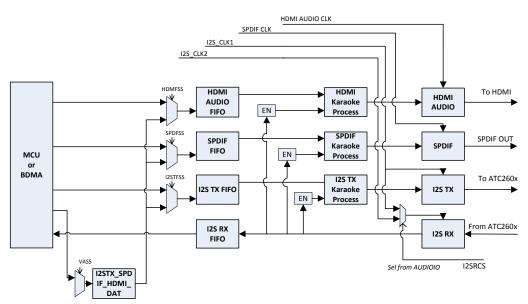

| :<br>:<br>:<br>:<br>:      | 23.1<br>23.2<br>23.3<br>23.4<br>Aud                                                                                                         | Over<br>Block<br>Func<br>Appl<br>lio In/                                              | view  C Diagram  tion Description  ication Note  Out Interface                                                                                                                                                                           | 195<br>195<br>196<br>196<br><b>197</b>                                                                              |

| :<br>:<br>:<br>:<br>:<br>: | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1                                                                                                 | Over<br>Block<br>Func<br>Appl<br>lio In/<br>Over<br>Block                             | view  c Diagram  tion Description  ication Note  Out Interface  view  c Diagram                                                                                                                                                          | 195<br>196<br>196<br><b>197</b><br>197                                                                              |

| :<br>:<br>:<br>:<br>:<br>: | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1                                                                                                 | Over Block Appl lio In/ Over Block Func                                               | view  diagram  tion Description  ication Note  Out Interface  view                                                                                                                                                                       | 195<br>196<br>196<br><b>197</b><br>197<br>198                                                                       |

| :<br>:<br>:<br>:<br>:<br>: | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3                                                                                 | Over Block Appl lio In/ Over Block Func                                               | view  C Diagram  tion Description  C Diagram  Out Interface  View  C Diagram  tion Description                                                                                                                                           | 195<br>196<br>196<br>197<br>197<br>198<br>198                                                                       |

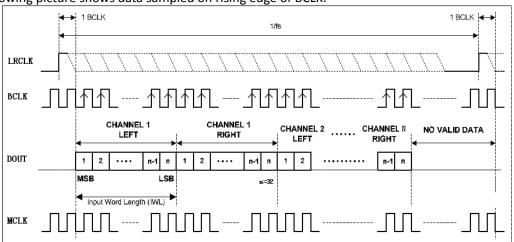

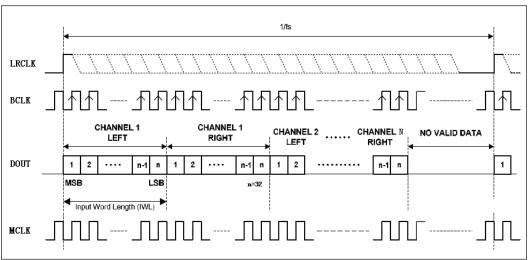

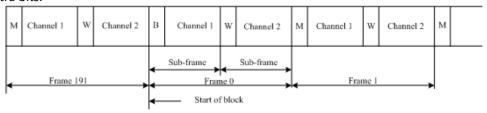

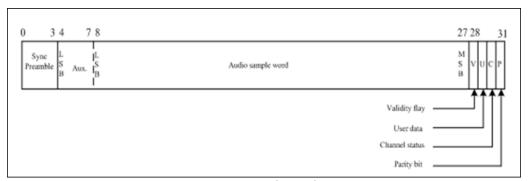

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3                                                                         | Over Block Appl lio In/ Over Block Func 3.1                                           | view  tion Description  ication Note  Out Interface  view  tion Description  12S Interface                                                                                                                                               | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>199                                                         |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3                                                                 | Over Block Appl lio In/ Over Block Func 3.1 3.2 Regis                                 | view  diagram  tion Description  cation Note  Out Interface  view  diagram  tion Description  12S Interface  SPDIF Interface  ster List                                                                                                  | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>199<br>200                                                  |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3                                                                         | Over Block Appl lio In/ Over Block Func 3.1 3.2 Regis                                 | view  C Diagram  tion Description  Dut Interface  View  C Diagram  tion Description  12S Interface  SPDIF Interface                                                                                                                      | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>199<br>200                                                  |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3<br>24.4                                                         | Over Block Appl lio In/ Over Block Func 3.1 3.2 Regis Regis 5.1                       | view  tion Description  ication Note  Out Interface  view  C Diagram  tion Description  I2S Interface  SPDIF Interface  ster List  ster Description                                                                                      | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>199<br>200<br>200<br>200                                    |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3<br>24.4<br>24.5<br>24.5                                         | Over Block Appl lio In/ Over Block Func 3.1 3.2 Regis Regis 5.1                       | view  tion Description  ication Note  Out Interface  view  tion Description  12S Interface  SPDIF Interface  ster List  ster Description  12S_CTL                                                                                        | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>199<br>200<br>200<br>201                                    |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3<br>24.3<br>24.4<br>24.5<br>24.5<br>24.5                         | Over Block Appl lio In/ Over Block Func 3.1 3.2 Regis 5.2 Regis 5.1 5.2               | view                                                                                                                                                                                                                                     | 195<br>196<br>196<br>197<br>197<br>198<br>198<br>199<br>200<br>200<br>201<br>202<br>202                             |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5 | Over Block Func Appl lio In/ Over Block Func 3.1 3.2 Regis 5.1 5.2 5.3 5.4 5.5        | view                                                                                                                                                                                                                                     | 195<br>196<br>196<br>197<br>197<br>198<br>198<br>199<br>200<br>200<br>201<br>202<br>202<br>202                      |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5 | Over Block Function In July 18 12 18 18 18 18 18 18 18 18 18 18 18 18 18              | view  tion Description  ication Note  Out Interface  view  c Diagram  tion Description  12S Interface  SPDIF Interface  ster List  cter Description  12S_CTL  12S_FIFOCTL  12STX_DAT  12SRX_DAT  SPDIF_HDMI_CTL  SPDIF_DAT               | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>199<br>200<br>200<br>201<br>202<br>202<br>202<br>202<br>204 |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5 | Over Block Function St. 1 St. 2 Regis 5.1 St. 2 St. 3 St. 4 St. 5 St. 6 St. 7         | view  tion Description  ication Note  Out Interface  view  c Diagram  tion Description  12S Interface  SPDIF Interface  ster List  ster Description  12S_CTL  12S_FIFOCTL  12STX_DAT  12SRX_DAT  SPDIF_HDMI_CTL  SPDIF_DAT  SPDIF_CLSTAT | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>199<br>200<br>200<br>201<br>202<br>202<br>202<br>204<br>204        |

| 24                         | 23.1<br>23.2<br>23.3<br>23.4<br>Aud<br>24.1<br>24.2<br>24.3<br>24.3<br>24.3<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5<br>24.5 | Over Block Appl lio In/ Over Block Func 3.1 3.2 Regis 5.1 5.2 5.3 5.4 5.5 5.6 5.7 5.8 | view  tion Description  ication Note  Out Interface  view  c Diagram  tion Description  12S Interface  SPDIF Interface  ster List  cter Description  12S_CTL  12S_FIFOCTL  12STX_DAT  12SRX_DAT  SPDIF_HDMI_CTL  SPDIF_DAT               | 195<br>196<br>196<br>197<br>197<br>197<br>198<br>199<br>200<br>200<br>201<br>202<br>202<br>204<br>204<br>204<br>204 |

|    | 24.5.          | 10   | I2STX_SPDIF_HDMI_CTL ·····    | 204 |

|----|----------------|------|-------------------------------|-----|

|    | 24.5.          | 11   | I2STX_SPDIF_HDMI_DAT ·····    | 205 |

| 2  | 24.6           | lqqA | ication Note ·····            | 205 |

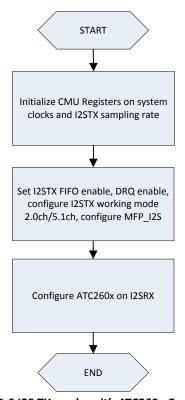

|    | 24.6.          |      | I2S TX operation              |     |

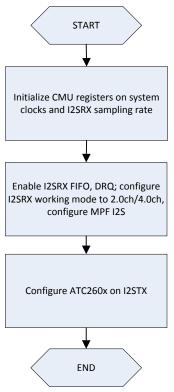

|    | 24.6.          | 2    | I2S RX operation ·····        | 206 |

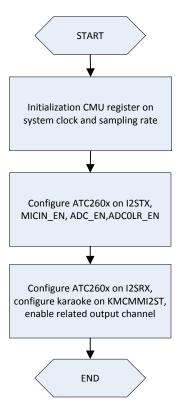

|    | 24.6.          | .3   | Karaoke operation ·····       | 206 |

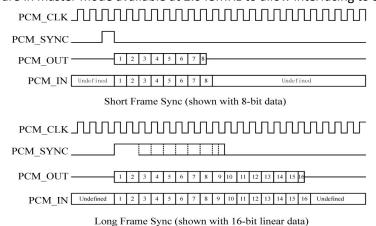

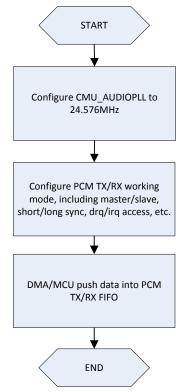

| 25 | PCM            | (Pul | se Code Modulation) ······    | 208 |

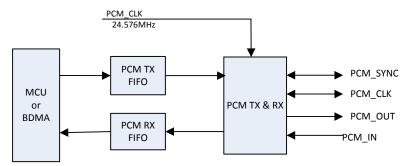

| 2  | 25.1           | Over | view·····                     | 208 |

| 2  | 25.2           | Bloc | k Diagram ······              | 208 |

| 2  | 25.3           |      | tion Description·····         |     |

| 2  | 25.4           |      | ster List ······              |     |

|    | 25.5           | _    | ster Description ·····        |     |

| -  | 25.5.          | _    | PCMx CTL                      |     |

|    | 25.5.          | 2    | PCMx_STAT ·····               | 210 |

|    | 25.5.          | .3   | PCMx_RXDAT ·····              |     |

|    | 25.5.          | 4    | PCMx_TXDAT ·····              | 211 |

| 2  | 25.6           | lqqA | ication Note ·····            | 211 |

|    | 25.6.          |      | Control Flow ····             |     |

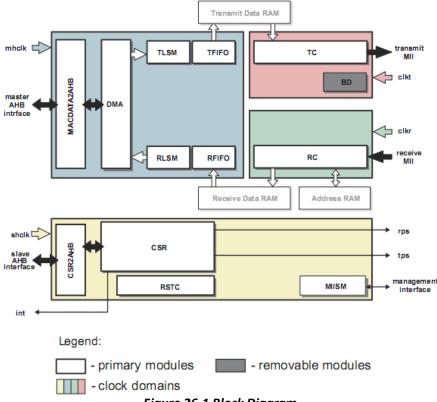

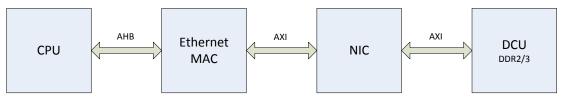

| 26 | Ethe           | rnet | MAC                           | 213 |